# Circuitos Electrónicos Digitales

Tema III

## Circuitos Combinacionales

**Universidad de Sevilla**

## Índice

- 1. Análisis de circuitos combinacionales

- 2. Diseño de circuitos combinacionales

- Análisis lógico: Dado un circuito, analizarlo consiste en encontrar:

- la expresión algebraica que implementa,

- su tabla de verdad y/o el k-mapa,

- explicación verbal de su función.

- Procedimiento:

- Se obtiene la función lógica realizada por las puertas cuyas entradas corresponden a las entradas primarias del circuito.

- Se obtiene la función lógica realizada en puertas con entradas conocidas (entradas primarias o salidas de puertas ya calculadas).

- Se repite el paso anterior hasta obtener la función de salida

- Se simplifica la expresión obtenida y/o se traduce a un mapa o tabla

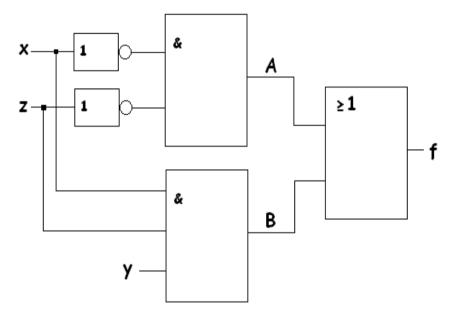

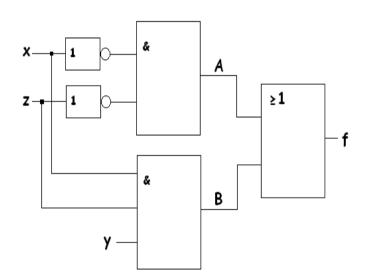

#### Circuito:

#### Expresión:

$$f(x,y,z) = A + B$$

$$A = \overline{x} \cdot \overline{z}$$

$$B = x \cdot y \cdot z$$

$$f(x,y,z) = x \cdot y \cdot z + \overline{x} \cdot \overline{z}$$

| xyz | f(x,y,z) |

|-----|----------|

| 000 | 1        |

| 001 | 0        |

| 010 | 1        |

| 011 | 0        |

| 100 | 0        |

| 101 | 0        |

| 110 | 0        |

| 111 | 1        |

$$f(x,y,z) = 1$$

si  $\begin{cases} xyz=1 & \text{si } x=y=z=1 \\ ó \\ \overline{x}\cdot\overline{z}=1 & \text{si } x=z=0 \end{cases}$  (0-0)

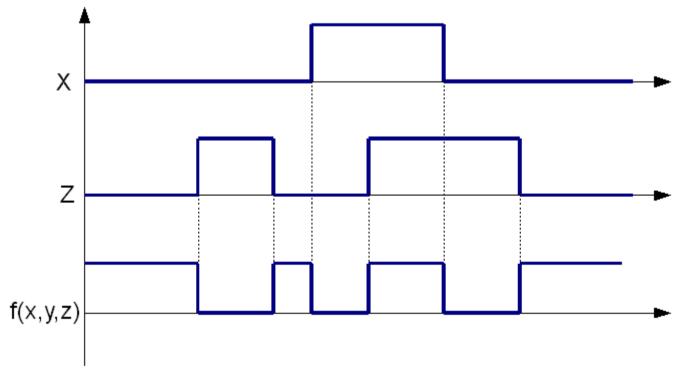

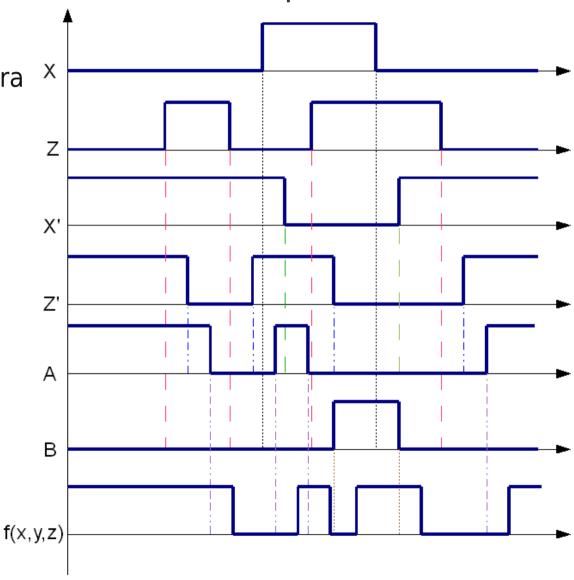

#### Análisis temporal:

- Representa la evolución en el tiempo de las entradas y salidas del circuito. A esta representación temporal se la denomina CRONOGRAMA.

- Dicha representación puede ser:

- Suponiendo que las puertas no tienen **retrasos**.

- Teniendo en cuenta los retrasos propios de las puertas lógicas.

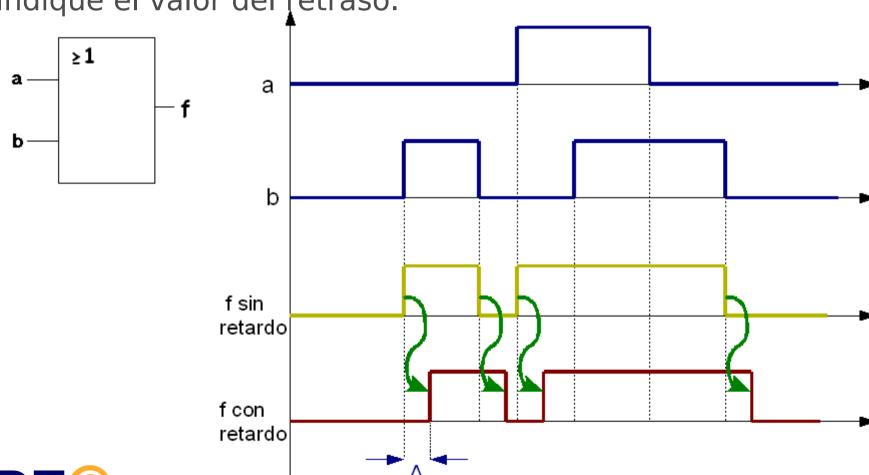

#### Azares:

Teniendo en cuenta los retrasos de la puertas podemos encontrarnos con la aparición de pequeños pulsos transitorios que hacen que la salida difiera de la esperada, es decir, de la obtenida de forma teórica sin considerar los retrasos.

#### Ejemplo de análisis temporal

#### Tabla:

| xyz | f(x,y,z) |

|-----|----------|

| 000 | 1        |

| 001 | 0        |

| 010 | 1        |

| 011 | 0        |

| 100 | 0        |

| 101 | 0        |

| 110 | 0        |

| 111 | 1        |

Cronograma (con y=1)

(sin considerar retrasos):

#### Ejemplo de análisis temporal

Para dibujar el cronograma considerando los retrasos, es necesario desplazar la salida de las puertas tanto como indique el valor del retraso.

#### Ejemplo de análisis temporal

Cronograma (con y=1)

(con retrasos igual para todas las puertas)

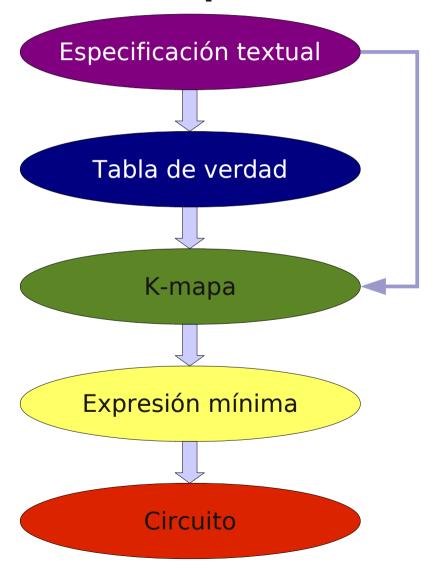

- El diseño (o síntesis) de un circuito es el proceso inverso al análisis: partiendo de una descripción inicial de la tarea que realiza el circuito, habrá de obtener:

- la tabla de verdad,

- el K-mapa,

- la ecuación booleana,

- el circuito.

#### Objetivos:

- El circuito debe ser óptimo, para ello se ha optado por considerar dos criterios de diseño:

- Reducir el número de puertas

- Reducir el número de conexiones

- Restricciones:

- Estructura en dos niveles (tres para simple raíl)

- Uso de puertas AND, OR, NAND y NOR

- No considerar fan-in ni fan-out como restricciones.

#### Pasos del proceso

#### Pasos del proceso

- Paso 1: Descripción textual → Tabla de verdad

- Determinar variables de entrada y especificar sus valores (0 y 1).

- Igual, para las variables de salida.

- Obtener la tabla de verdad.

- Paso 2: Obtener el K-mapa

- A partir de la tabla de verdad anterior o de la especificación establecida, se obtiene el K-mapa de la función a implementar.

#### Ejemplo:

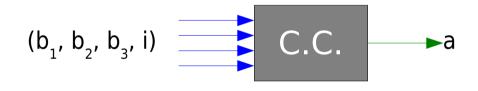

Se desea diseñar un circuito combinacional que recibe información del estado de tres bombillas (encendida o apagada) y del estado de un único interruptor (on - off). El circuito debe generar una alarma que se active cuando alguna de las bombillas no esté encendida cuando el interruptor está on, o cuando alguna bombilla esté encendida y el interruptor esté off.

Entradas: tres bombillas, interruptor Salida: Alarma

$$b_i = \begin{cases} 0 \text{ apagada} & i = \begin{cases} 0 \text{ off} \\ 1 \text{ encendida} & 1 \text{ on} \end{cases}$$

$$a = \begin{cases} 0 \text{ inactiva} \\ 1 \text{ activa} & 1 \text{ on} \end{cases}$$

| ib <sub>1</sub> b <sub>2</sub> b <sub>3</sub> | a | i b <sub>1</sub> b <sub>2</sub> b <sub>3</sub> | a |

|-----------------------------------------------|---|------------------------------------------------|---|

| 0000                                          | 0 | 1000                                           | 1 |

| 0001                                          | 1 | 1001                                           | 1 |

| 0010                                          | 1 | 1010                                           | 1 |

| 0011                                          | 1 | 1011                                           | 1 |

| 0100                                          | 1 | 1100                                           | 1 |

| 0101                                          | 1 | 1101                                           | 1 |

| 0110                                          | 1 | 1110                                           | 1 |

| 0111                                          | 1 | 1111                                           | 0 |

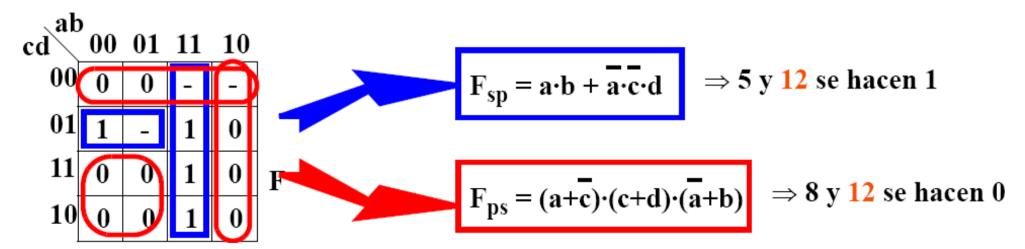

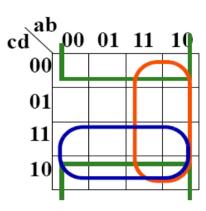

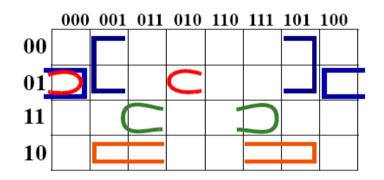

#### Diseño con K-mapa

- Paso 3: Obtener la expresión mínima

- Para obtener la expresión mínima de una función que nos permita implementar un diseño en dos niveles utilizaremos el k-mapa.

- Nos centramos en obtener una expresión mínima como suma de productos. (1's lógicos).

- De manera análoga se consigue una expresión como producto de sumas, considerando los 0's lógicos.

- Un 1 en el K-mapa representa un término producto (mintérmino).

- La idea es ir agrupando 1's para conseguir menos términos productos y con menos variables. Para ello, nos basamos en el concepto de implicante (implicada).

#### **Implicante**

- Es un 1 o grupo de 1's representado en el K-mapa. Los grupos deben estar formado por una potencia de 2 de 1's, y estos deben ser vecinos.

- Los grupos se van formando a partir de grupos de tamaño inmediatamente inferior. Por ejemplo, agrupamos dos 1's vecinos para formar un grupo de dos 1's. Luego, este grupo podemos agruparlo con otro vecino formado por otros dos 1's, para obtener un grupo de 4.

- El número de 1´s del grupo determina el orden del implicante.

- El orden del implicante está relacionado con el número de variables que posee la expresión del término producto que lo representa.

#### Diseño con K-mapa: Implicante

| Orden | Nº de 1's         | Nº variables | Ejemplo    | 5 var.  |

|-------|-------------------|--------------|------------|---------|

| Orden | Nº GE IS          |              | Implicante | Cuantas |

| 0     | 1=20              | n            | ab'cd'e    | 32      |

| 1     | 2=21              | n - 1        | ab'd'e     | 80      |

| 2     | 4=2 <sup>2</sup>  | n - 2        | ab'e       | 80      |

| 3     | 8=2 <sup>3</sup>  | n - 3        | b'e        | 40      |

| 4     | 16=24             | n - 4        | b'         | 10      |

| 5     | 32=2 <sup>5</sup> | n - 5        | 1          | 1       |

| k     | $m=2^k$           | n - k        |            |         |

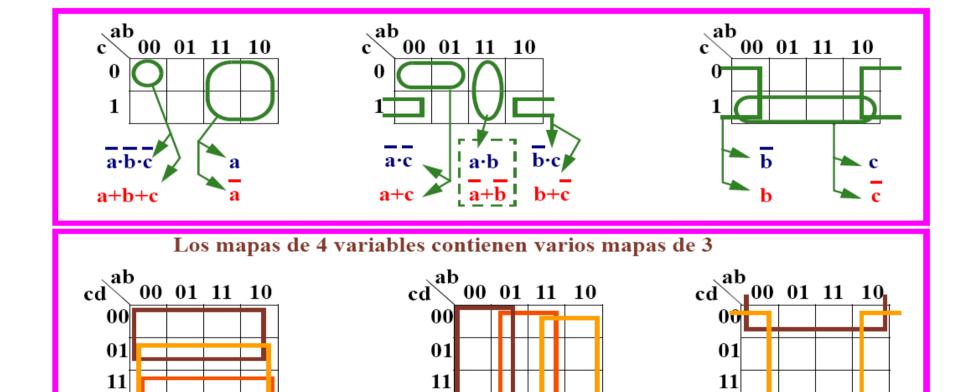

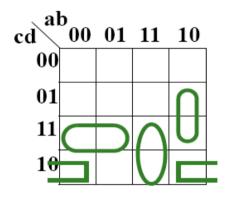

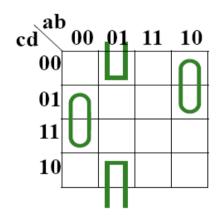

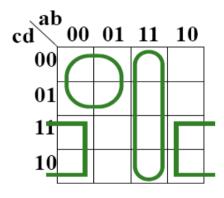

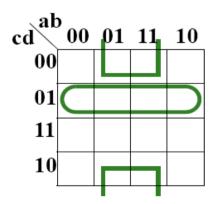

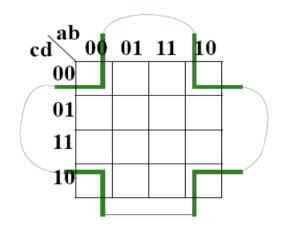

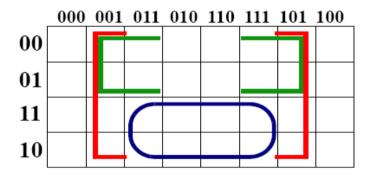

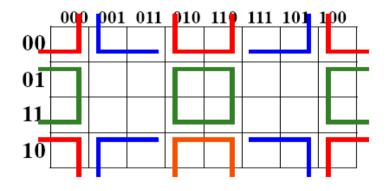

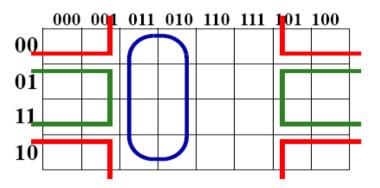

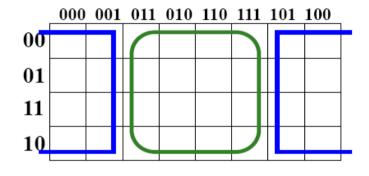

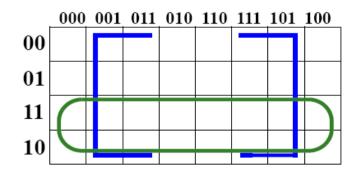

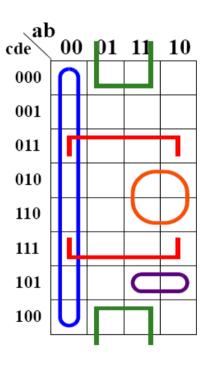

#### Agrupaciones posibles

10

10

10

#### Agrupaciones posibles

#### Agrupaciones posibles

### Agrupaciones posibles

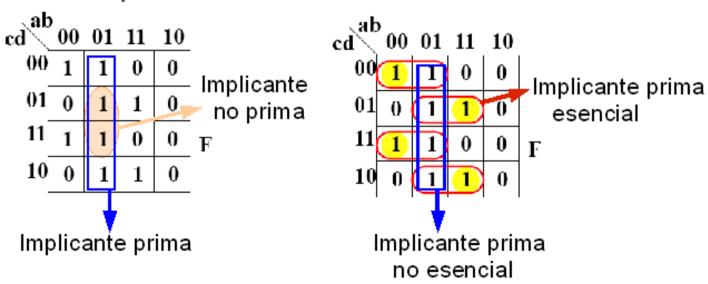

#### Diseño con K-Mapa: Definiciones

- Una Implicante se dice que es prima si no está cubierta por ninguna otra implicante de la función.

- Una implicante prima se dice que es esencial si cubre algún mintérmino no incluido en ninguna otra implicante prima.

#### Diseño con K-mapa: Expresión mínima

- La expresión mínima se obtiene sumando un conjunto de implicantes primas, que:

- Contenga el menor número de implicantes primas que cubran completamente la función.

- Contengan el menor número de literales.

- Todas las implicantes primas de la función están en dicha expresión.

- El menor número de literales se obtiene eligiendo las implicantes de mayor orden.

Diseño con k-mapa: Funciones incompletamente especificadas

- Las casillas con inespecificación se usan como mejor nos convenga:

- Se pueden incluir para formar grupos mayores.

- No es necesario cubrirlas todas.

Ejemplo:  $F = \Sigma (1, 13, 14, 15) + d(5, 8, 12)$