# Circuitos electrónicos digitales Unidades Aritméticas Lógicas

## Índice

- Introducción

- Circuitos sumadores básicos

- Sumador paralelo de n bits

- Sumador/Restador

- Unidad aritmético-lógica (ALU)

#### Introducción

- Los sistemas digitales poseen una gran potencia de cálculo ya que permiten ejecutar con gran velocidad operaciones aritméticas y lógicas

- Una operación aritmética en un computador puede ser realizada de dos formas:

- software: existe un algoritmo que descompone esa operación en otras más elementales que son realizadas mediante hardware

- Aritmética binaria

- Coma flotante

#### Introducción

- Hardware aritmético en los procesadores:

- □ Todos los procesadores poseen al menos un sumadorrestador

- Software aritmético en los procesadores:

- ⇒ A medida que aumenta la complejidad se incluyen instrucciones de multiplicación y división

- En los más complejos se tienen operaciones más abstractas como exponenciales, logaritmos, etc.

#### Introducción

- Las principales diferencias entre la forma de operar manual y la de un computador digital son:

- $\Rightarrow$  La base del sistema de numeración es B = 2 (binaria).

- La forma de representar números con signo normalmente no es con signo-magnitud, sino a través de los complementos (a 2 o a 1).

- ⇒ El número de bits de los datos está acotado entonces:

- ✓ Errores de desbordamiento, de precisión

- ✓ Incumplimiento de propiedades algebráicas: las operaciones se vuelven no-cerradas

- ✓ Pueden incumplirse las propiedades asociativas y distributiva).

## Índice

- Introducción

- Circuitos sumadores básicos

- Sumador paralelo de n bits

- Sumador/Restador

- Unidad aritmético-lógica (ALU)

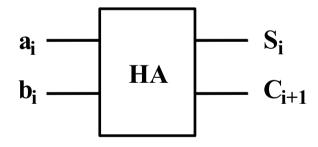

- Semisumador o Half Adder (HA)

- ⇒ Se trata del circuito que suma dos bits.

- Obtiene como salida el bit de suma y el acarreo.

| a <sub>i</sub> | b <sub>i</sub> | $C_{i+1}$ | Si |

|----------------|----------------|-----------|----|

| 0              | 0              | 0         | 0  |

| 1              | 0              | 0         | 1  |

| 0              | 1              | 0         | 1  |

| 1              | 1              | 1         | 0  |

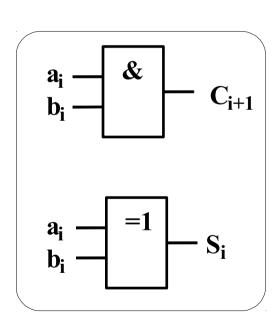

- Semisumador o Half Adder (HA)

- Una posible implementación mediante puertas lógicas

$$C_{i+1} = a_i \cdot b_i$$

$$S_i = a_i \oplus b_i$$

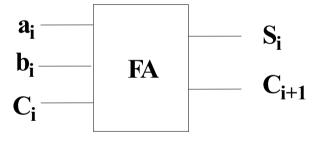

- Sumador completo Full Adder (FA)

- ⇒ Permite realizar la suma de tres bits simultáneamente.

- ⇒ Obtiene como salida el bit de suma y el acarreo.

| $\mathbf{a_i}$ | $\mathbf{b_i}$ | $C_{\mathbf{i}}$ | $C_{i+1}$ | $S_i$ |

|----------------|----------------|------------------|-----------|-------|

| 0              | 0              | 0                | 0         | 0     |

| 0              | 0              | 1                | 0         | 1     |

| 0              | 1              | 0                | 0         | 1     |

| 0              | 1              | 1                | 1         | 0     |

| 1              | 0              | 0                | 0         | 1     |

| 1              | 0              | 1                | 1         | 0     |

| 1              | 1              | 0                | 1         | 0     |

| 1              | 1              | 1                | 1         | 1     |

|                |                |                  |           |       |

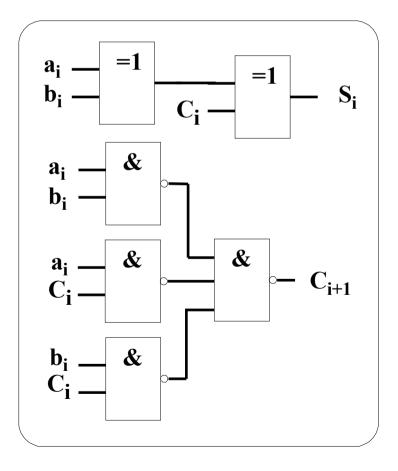

- Sumador completo Full Adder (FA)

- Una implementación mediante puertas lógicas

$$C_{i+1} = a_i \cdot b_i + a_i \cdot C_i + b_i \cdot C_i$$

$$S_i = a_i \oplus b_i \oplus C_i$$

## Índice

- Introducción

- Circuitos sumadores básicos

- Sumador paralelo de n bits

- Sumador/Restador

- Unidad aritmético-lógica (ALU)

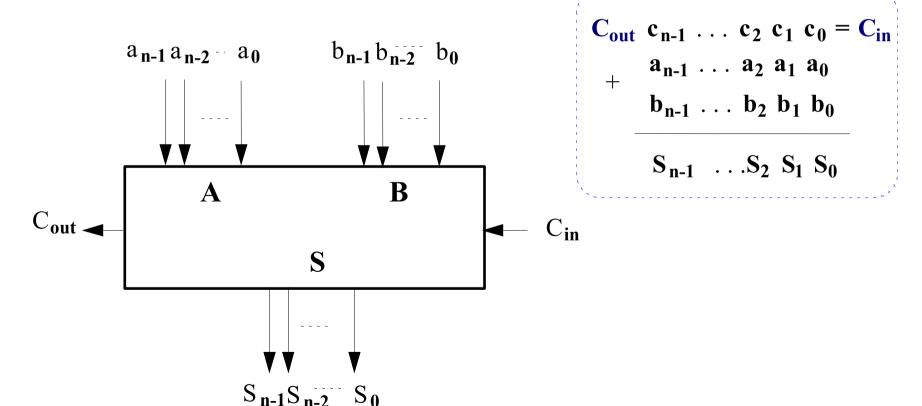

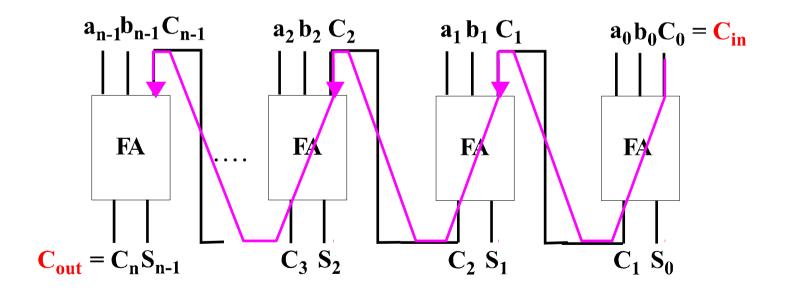

Un sumador paralelo de n bits, es un dispositivo lógico combinacional de 2n+1 entradas y n+1 salidas que realiza la suma de dos números binarios de n bits.

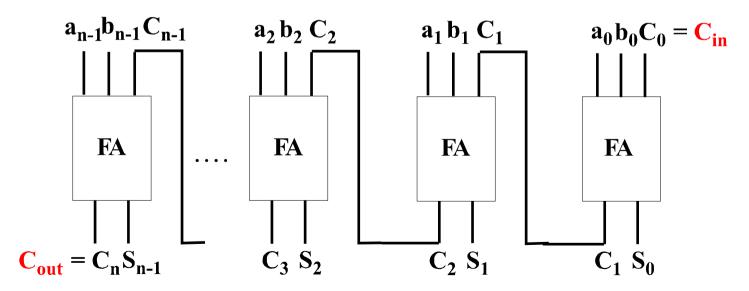

- Sumador paralelo con acarreo serie

- ⇒ Es el más intuitivo y tiene un coste razonablemente bajo.

- ➡ También es conocido como sumador de rizado o ripple adder

- Se trata de un circuito modular

- Es lento debido a la propagación serie del acarreo

- El tiempo que tarda en realizarse una suma crece linealmente con el número de bits

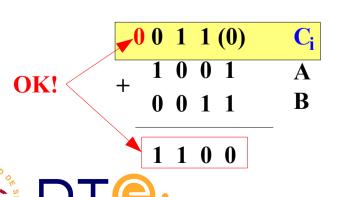

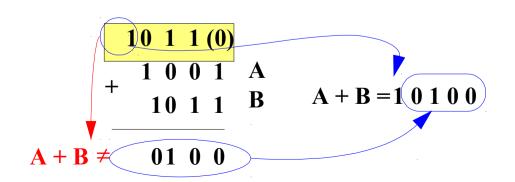

- El problema del desbordamiento en la suma de magnitudes

- Con n bits el rango representable es [0,2n-1]

- ⇒ Si A+B > 2n-1

- el resultado no es representable

- ✓ hay desbordamiento (overflow)

- Cout señala la existencia de desbordamiento

- ⇒ En caso de desbordamiento, el resultado correcto está en el número de n+1 bits (A + B = CoutSn-1 .... S0)

## Índice

- Introducción

- Circuitos sumadores básicos

- Sumador paralelo de n bits

- Sumador/Restador

- Unidad aritmético-lógica (ALU)

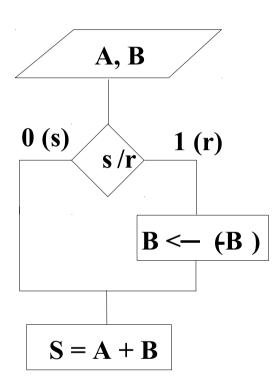

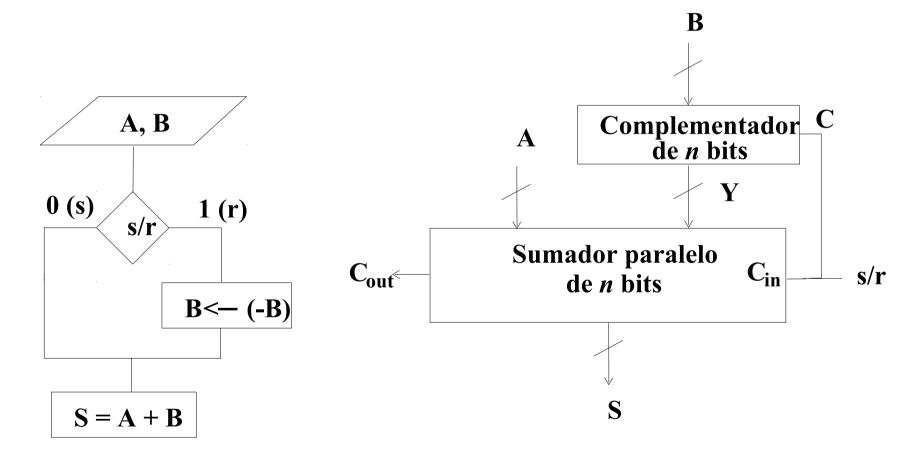

- La suma-resta de números con signo

- Calcular la diferencia A-B es equivalente a calcular A + (-B)

- ✓ la resta aritmética se reduce a una suma

- ✓ implica trabajar con números con signo

- ⇒ B es (- B) en complemento a 1

- ⇒ [B + 1] es (- B) en complemento a 2

- La suma-resta de números en complemento a 2

- $\Rightarrow$  En general: A B = A + (-B)

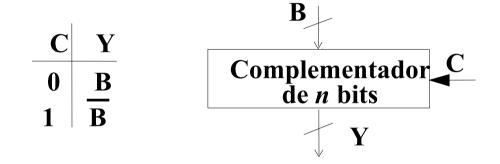

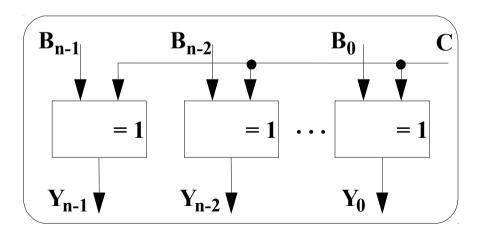

El complementador es simplemente una colección de puertas XOR

- La suma-resta de números en complemento a 2

- Utilizaremos la notación complemento a 2 para representar los números positivos y negativos

$$\begin{array}{r}

1001 = -7 \\

\hline

0101 = +5 \\

\hline

1110 = -2

\end{array}$$

$$11 00 = -4$$

$$1111 = -1$$

$$11011 = -5$$

$$\begin{array}{r}

11\ 00 = -4 \\

\hline

0100 = +4 \\

\hline

1\ 0000 = 0

\end{array}$$

$$0101 = +5$$

$$0100 = +4$$

$$1001 = -7$$

$$0011 = +3$$

$0100 = +4$

$0111 = +7$

$$1001 = -7

1010 = -6

10011 = +3$$

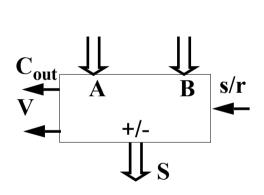

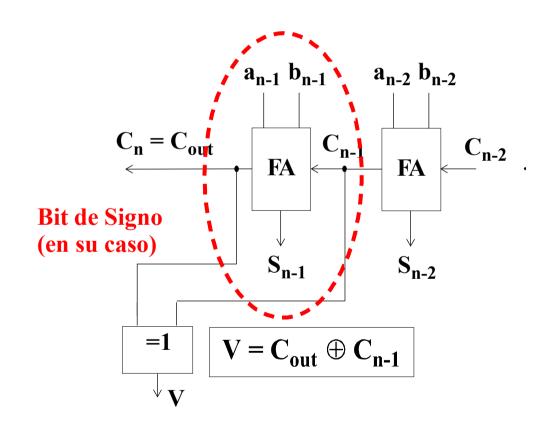

- El problema del desbordamiento en la suma-resta de números con signo

- Se pone de manifiesto porque la magnitud ocupa un bit más y el bit de signo no es correcto

- Problema de desbordamiento en la suma-resta de números con signo. En la suma, el desbordamiento se produce cuando:

- al sumar dos números positivos se obtiene uno negativo

- al sumar dos números negativos se obtiene uno positivo

$$V = C_{out} \oplus C_{n-1}$$

#### El sumador restador quedaría:

## Índice

- Introducción

- Circuitos sumadores básicos

- Sumador paralelo de n bits

- Sumador/Restador

- Unidad aritmético-lógica (ALU)

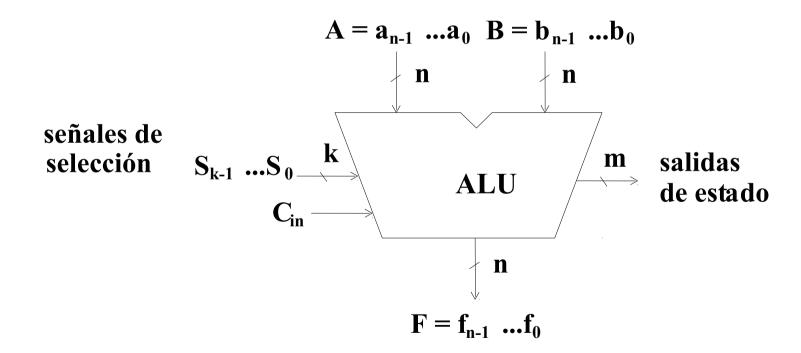

- Es el circuito donde se realiza el procesado de datos

- Procesado: operaciones aritméticas y lógicas.

Normalmente se opera sobre dos datos

- Usualmente pueden realizar diversas operaciones.

Para elegirlas se incluyen unas señales de selección

- Además de las salidas que muestran el resultado de la operación, se incluyen otras salidas (flags) de estado o de condición.

- Típicamente son C<sub>out</sub>, V, Z (Z=1 si el resultado es 0) y

S (signo)

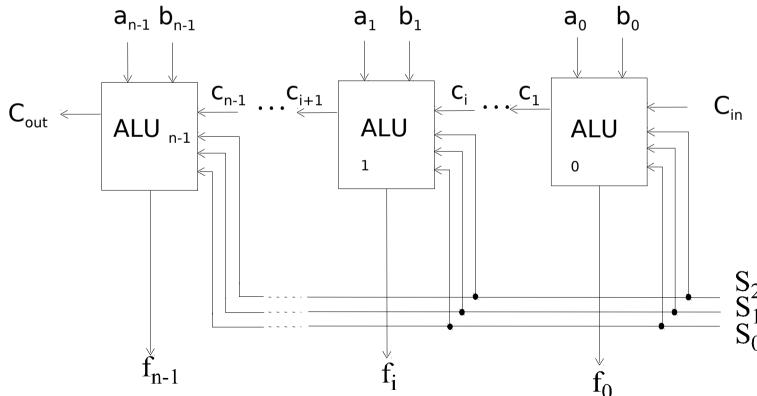

#### Representación gráfica de una ALU

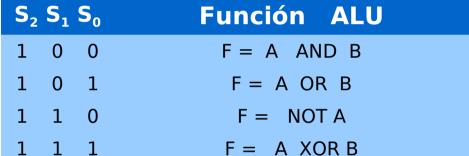

#### Ejemplo de una ALU

| S <sub>2</sub> S <sub>1</sub> S <sub>0</sub> | Función ALU            |                            |  |  |

|----------------------------------------------|------------------------|----------------------------|--|--|

|                                              | $C_{in} = 0$           | $C_{in} = 1$               |  |  |

| 0 0 0                                        | F = A                  | F = A + 1                  |  |  |

| 0 0 1                                        | F = A + B              | F = A + B + 1              |  |  |

| 0 1 0                                        | $F = A + \overline{B}$ | $F = A + \overline{B} + 1$ |  |  |

| 0 1 1                                        | F = A - 1              | F = A                      |  |  |

| 1 0 0                                        | F = A AND B            |                            |  |  |

| 1 0 1                                        | F = A OR B             |                            |  |  |

| 1 1 0                                        | F = NOT A              |                            |  |  |

| 1 1 1                                        | F = A XOR B            |                            |  |  |

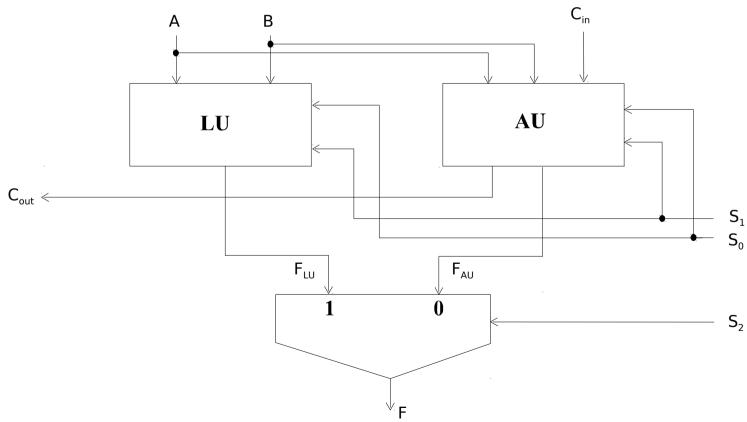

- Realización de una ALU

- ⇒ Se separan las partes aritmética (AU) y lógica (LU).

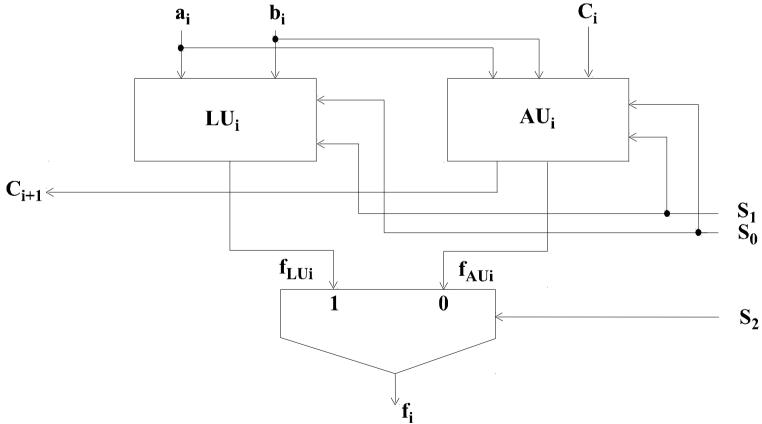

- Realización de una ALU

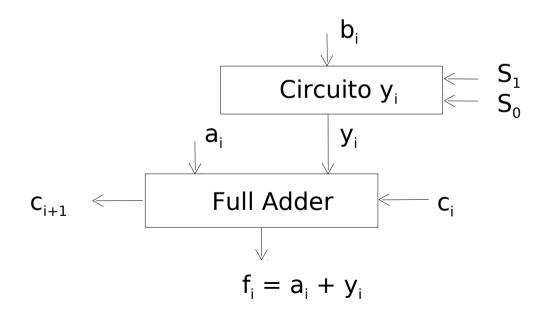

- Implica la realización de la ALU para cada pareja de bits entrantes (etapa típica)

- Realización de una ALU

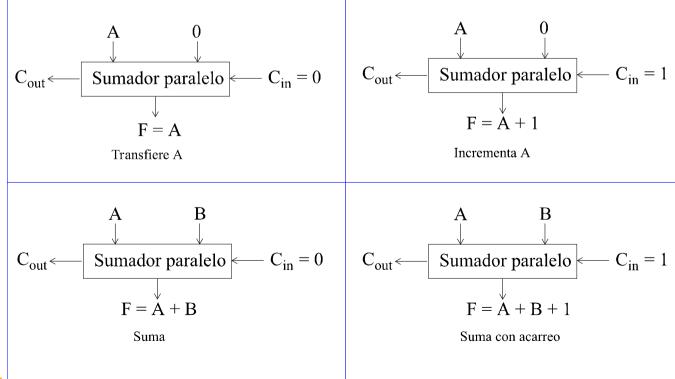

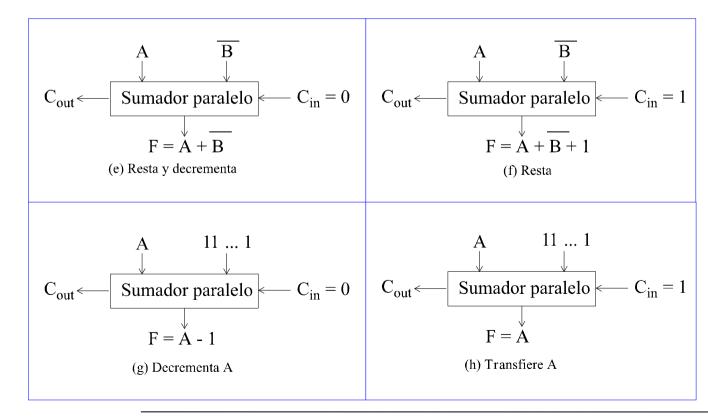

- Diseño de la Unidad Aritmética

- El bloque aritmético consta básicamente de un sum paralelo

- Para obtener las diferentes operaciones se ha de modificar los datos de entrada al sumador

- Diseño de la Unidad Aritmética

- El bloque aritmético consta básicamente de un sum paralelo

- Para obtener las diferentes operaciones se ha de modificar los datos de entrada al sumador

- Diseño de la Unidad Aritmética

- El bloque aritmético consta básicamente de un sum paralelo

- Para obtener las diferentes operaciones se ha de modificar los datos de entrada al sumador

| S <sub>2</sub> S <sub>1</sub> S <sub>0</sub> | Función ALU            |   |              |                            |   |         |

|----------------------------------------------|------------------------|---|--------------|----------------------------|---|---------|

|                                              | $C_{in} = 0$           |   | $C_{in} = 1$ |                            |   |         |

| 0 0 0                                        | F = A                  | Α | 0            | F = A + 1                  | А | 0       |

| 0 0 1                                        | F = A + B              | Α | В            | F = A + B + 1              | А | В       |

| 0 1 0                                        | $F = A + \overline{B}$ | А | NOT (B)      | $F = A + \overline{B} + 1$ | А | NOT (B) |

| 0 1 1                                        | F = A - 1              | Α | 111          | F = A                      | А | 111     |

- Diseño de la Unidad Aritmética

- El bloque aritmético consta básicamente de un sum paralelo

- ⇒ Para obtener las diferentes operaciones se ha de modificar los datos de entrada al sumador

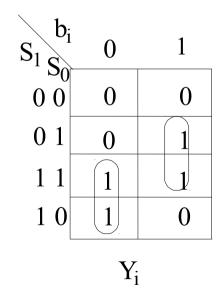

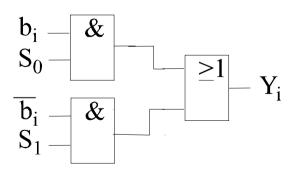

Diseño del "circuito yi" con puertas lógicas

| $S_1S_0$ | Yi                                   |

|----------|--------------------------------------|

| 0 0      | 0                                    |

| 0 1      | b <sub>i</sub>                       |

| 10       | $\overline{\mathbf{b}}_{\mathbf{i}}$ |

| 11       | 1                                    |

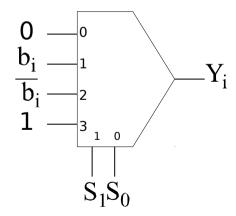

Diseño del "circuito yi" con un multiplexor

| $S_1S_0$ | $Y_i$                                |

|----------|--------------------------------------|

| 0 0      | 0                                    |

| 0 1      | b i                                  |

| 10       | $\overline{\mathbf{b}}_{\mathbf{i}}$ |

| 11       | 1                                    |

El acarreo de salida nos puede dar una información muy importante

| S <sub>1</sub> S <sub>0</sub> C <sub>in</sub> |          | Operación         | C <sub>out</sub> =1 si | Comentario                                          |

|-----------------------------------------------|----------|-------------------|------------------------|-----------------------------------------------------|

| 0 0 0                                         | F=A      | Transferir A      |                        | C <sub>out</sub> =0 siempre                         |

| 0 0 1                                         | F=A+1    | Incrementar A     | A=2 <sup>n</sup> -1    | Si C <sub>out</sub> =1 , F=0                        |

| 0 1 0                                         | F=A+B    | Sumar A+B         | A+B≥2 <sup>n</sup>     | Overflow si C <sub>out</sub> =1                     |

| 0 1 1                                         | F=A+B+1  | Incrementar A+B   | A+B≥2 <sup>n</sup> -1  | Overflow si C <sub>out</sub> =1                     |

| 1 0 0                                         | F=A+B'   | Restar A-B en Ca1 | A>B                    | Si $C_{out} = 0 \rightarrow A \le B y F = Ca1(B-A)$ |

| 1 0 1                                         | F=A+B'+1 | Restar A-B en Ca2 | A≥B                    | Si $C_{out} = 0 \rightarrow A < B y F = Ca1(B-A)$   |

| 1 1 0                                         | F=A-1    | Decrementar A     | A≠0                    | Si $C_{out} = 0 \rightarrow A = 0$                  |

| 1 1 1                                         | F=A      | Transferir A      |                        | C <sub>out</sub> =1 siempre                         |

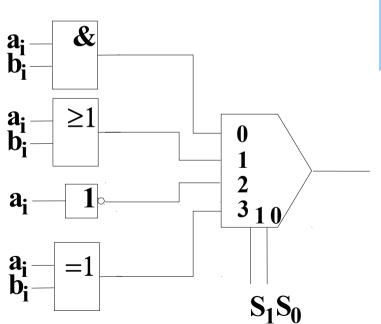

- Diseño de la Unidad Lógica

- Diseño de la etapa típica con un multiplexor y puertas lógicas

$f_{LUi}$