## Tarea 7

**Ejercicio 1.** Diseñe un circuito aritmético con una entrada x de 8 bits y una salida z de 8 bits tal que z = x + 79. Emplee circuitos sumadores básicos para el diseño. Añada una salida de desbordamiento.

**Ejercicio 2.** Diseñe un circuito aritmético con una entrada x de 8 bits y una saliza z de 8 bits tal que z = 6 \* x. Emplee un sólo sumador de magnitudes. Añada una salida de desbordamiento.

**Ejercicio 3.** Calcule el mínimo número de bits para hacer las siguientes operaciones en complemento a 2. Realice las operaciones en binario y compruebe el resultado operando en decimal.

a)

$$(+42) + (-13)$$

**Ejercicio 4.** Diseñe un sumador de 8 bits de número con/sin signo que tenga salida de desbordamiento. El desbordamiento debe indicar esta condición de forma correcta dependiendo si se opera con números con signo (complemento a 2) o sin signo. Las señales de entrada y salida son:

- a, b: datos de entrada.

- u: tipo de entrada (0-con signo, 1-sin signo).

- z: resultado de la suma.

- ov: salida de desbordamiento (0-no desbordamiento, 1-desbordamiento).

Implemente el circuito usando FA, HA y puertas lógicas y/o subsistemas.

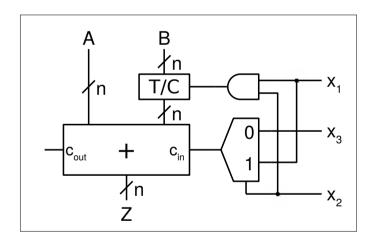

**Ejercicio 5.** En el circuito de la figura hay, entre otros, un sumador paralelo de n bits y un bloque "transfiere/complementa" (T/C). Describa funcionalmente el circuito. Esto es, represente su operación en forma de tabla y explíquelo verbalmente.

| op[2:0] | Operation    | Z     |

|---------|--------------|-------|

| 000     | Addition     | a + b |

| 001     | Substraction | a - b |

| 010     | Increment 1  | a + 1 |

| 011     | Decrement 1  | a - 1 |

| 100     | Increment 2  | a + 2 |

| 101     | Decrement 2  | a - 2 |

| 110     | Increment 4  | a + 4 |

| 111     | Decrement 4  | a - 4 |

**Ejercicio 6.** Diseñe una unidad aritmética con las operaciones indicadas en la tabla. Incluya una salida de desbordamiento (ov). Realice el diseño empleando FA, HA y puertas lógicas o subsistemas según necesidad.

**Ejercicio 7.** (Trabajo voluntario) Describa en Verilog el circuito que se pide en el ejercicio 2. Puede emplear para su descripción operadores de suma y desplazamiento de bits, pero no de producto. Realice un banco de pruebas para comprobar su operación.

**Ejercicio 8.** (Trabajo voluntario) Describa y simule en Verilog la unidad aritmética del ejercicio 6. Use los ejemplos de la unidad 5 de *curso-verilog.v* $^1$  como referencia.