# Unidades aritméticas y lógicas

#### DAPA E.T.S.I. Informática Universidad de Sevilla Noviembre, 2015

Jorge Juan <jjchico@dte.us.es> 2010-2015

Esta obra esta sujeta a la Licencia Reconocimiento-CompartirIgual 4.0 Internacional de Creative Commons. Para ver una copia de esta licencia, visite http://creativecommons.org/licenses/by-sa/4.0/ o envíe una carta Creative Commons, PO Box 1866, Mountain View, CA 94042, USA.

Departamento de Tecnología Electrónica - Universidad de Sevilla

#### **Contenidos**

- Introducción

- · Aritmética binaria

- · Circuitos sumadores básicos

- · Sumador de magnitudes

- · Números binarios con signo

- Sumador con signo. Desbordamiento

- Sumador/restador

- ALU

#### Introducción

- Los circuitos aritméticos hacen operaciones aritméticas sobre datos de n bits: +, -, \*, /

- Las operaciones aritméticas son las más importantes en los sistemas digitales (computadores)

- Dos formas de hacer operaciones aritméticas en los computadores:

- En hardware (mediante circuitos específicos): tradicionalmente sólo para operaciones simples (suma, producto, etc.)

- En software (mediante programación): tradicionalmente para operaciones complejas (división, funciones trigonométricas, etc.)

Departamento de Tecnología Electrónica - Universidad de Sevilla

# Soporte aritmético hardware en ordenadores personales

- 1970-1980 (procesadores de 8 bits)

- Sólo suma y resta de números enteros.

- 1980-1990 (procesadores de 16 bits)

- Multiplicadores y divisores

- Co-procesadores matemáticos como opción

- Número reales, funciones complejas, etc.

- 1990-2000 (procesadores de 32 bits)

- Co-procesadores integrados

- Múltiples unidades de enteros: varios cálculos a la vez

- Operaciones de soporte multimedia

- Operaciones para gráficos 2-D (en controladores gráficos)

- 2000- (procesadores de 64 bits)

- Operaciones matemáticas avanzadas

- Procesamiento digital, simulación física, etc.

- Operaciones para gráficos 3D (en controladores gráficos)

#### **Contenidos**

- Introducción

- · Aritmética binaria

- · Circuitos sumadores básicos

- Sumador de magnitudes

- Números binarios con signo

- Sumador con signo. Desbordamiento

- Sumador/restador

- ALU

Departamento de Tecnología Electrónica - Universidad de Sevilla

#### Aritmética binaria

- Aritmética usada en sistemas digitales (computadores)

- Basada en el sistema de numeración en base 2

- Número fijo de bits

Departamento de Tecnología Electrónica - Universidad de Sevilla

#### Aritmética binaria

- Ejemplo

- A = 100110

- -B = 1101

- Operaciones

- -A+B

- A B

- A \* B

- A/B

Departamento de Tecnología Electrónica - Universidad de Sevilla

#### **Contenidos**

- Introducción

- · Aritmética binaria

- Circuitos sumadores básicos

- Sumador de magnitudes

- Números binarios con signo

- Sumador con signo. Desbordamiento

- Sumador/restador

- ALU

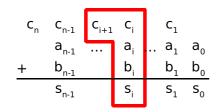

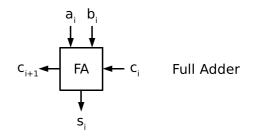

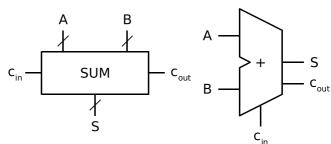

# Circuitos sumadores básicos. Sumador completo (*full adder*)

| a <sub>i</sub> | $b_{i}$ | c <sub>i</sub> | $C_{i+1}$ | S <sub>i</sub> |

|----------------|---------|----------------|-----------|----------------|

| 0              | 0       | 0              | 0         | 0              |

| 0              | 0       | 1              | 0         | 1              |

| 0              | 1       | 0              | 0         | 1              |

| 0              | 1       | 1              | 1         | 0              |

| 1              | 0       | 0              | 0         | 1              |

| 1              | 0       | 1              | 1         | 0              |

| 1              | 1       | 0              | 1         | 0              |

| 1              | 1       | 1              | 1         | 1              |

Departamento de Tecnología Electrónica - Universidad de Sevilla

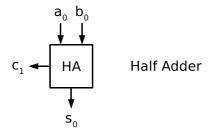

# Circuitos sumadores básicos. Semi sumador (*half adder*)

| $a_0$ | b <sub>o</sub> | $c_{_1}$ | S <sub>0</sub> |

|-------|----------------|----------|----------------|

| 0     | 0              | 0        | 0              |

| 0     | 1              | 0        | 1              |

| 1     | 0              | 0        | 1              |

| 1     | 1              | 1        | 0              |

$$\begin{aligned}

s_0 &= a_0 \oplus b_0 \\

c_1 &= a_0 b_0

\end{aligned}$$

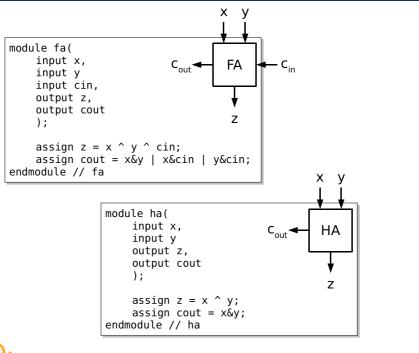

# FA y HA. Descripciones en Verilog

U DTO

Departamento de Tecnología Electrónica - Universidad de Sevilla

#### **Contenidos**

- Introducción

- · Aritmética binaria

- · Circuitos sumadores básicos

- Sumador de magnitudes

- · Números binarios con signo

- · Sumador con signo. Desbordamiento

- Sumador/restador

- ALU

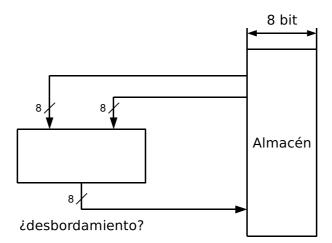

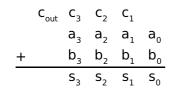

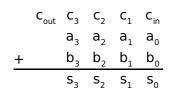

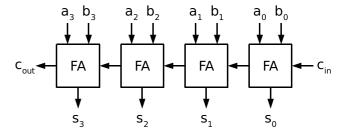

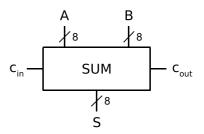

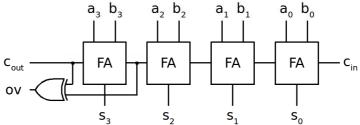

# Sumador de magnitudes de n bits

$$S = (A + B) \mod 2^n$$

$c_{\text{out}}$  es un indicador de "desbordamiento" ( $\emph{overflow}$ ): el resultado no puede represetnarse con los bits disponibles (n).

Departamento de Tecnología Electrónica - Universidad de Sevilla

# Sumador de magnitudes de n bits con entrada de acarreo

$$S = (A + B + C_{in}) \mod 2^n$$

$c_{_{in}}$  es útil para conectar varios sumadores y sumar números de más de n bits.

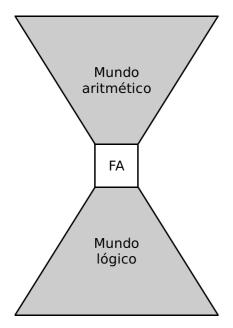

# Importancia del sumador completo (FA)

- El sumador completo hace la operación aritmética más básica (sumar 3 bits) usando sólo operadores lógicos.

- "El sumador completo es el punto de encuentro entre el mundo lógico de los sistemas digitales y el mundo aritmético de los computadores" J. Juan

Departamento de Tecnología Electrónica - Universidad de Sevilla

# **Ejemplos Verilog**

#### Usando sumadores completos (FA)

```

module adder8_fa(

input [7:0] a,

input [7:0] b,

input cin,

output [7:0] s,

output cout

);

// auxiliary signal

wire [7:1] c;

fa fa0 (a[0], b[0], cin, s[0], c[1]);

fa fa1 (a[1], b[1], c[1], s[1], c[2]);

fa fa2 (a[2], b[2], c[2], s[2], c[3]);

fa fa3 (a[3], b[3], c[3], s[3], c[4]);

fa fa4 (a[4], b[4], c[4], s[4], c[5]);

fa fa5 (a[5], b[5], c[5], s[5], c[6]);

fa fa6 (a[6], b[6], c[6], s[6], c[7]);

fa fa7 (a[7], b[7], c[7], s[7], cout);

endmodule // adder8_fa

```

#### Usando operadores aritméticos

```

module adder8(

input [7:0] a,

input [7:0] b,

input cin,

output [7:0] s,

output cout

);

assign

{cout, s} = a+b+cin;

endmodule // adder8

```

#### **Contenidos**

- Introducción

- · Aritmética binaria

- · Circuitos sumadores básicos

- · Sumador de magnitudes

- Números binarios con signo

- · Sumador con signo. Desbordamiento

- Sumador/restador

- ALU

Departamento de Tecnología Electrónica - Universidad de Sevilla

# ¿Y los números negativos? Números binarios con signo

- En los circuitos digitales no hay "signo", sólo ceros y unos.

- El signo debe codificarse mediante bits junto con la palabra que representa al número.

- Hay varias alternativas para codificar números con signo:

- Representación signo-magnitud

- Representación en exceso

- Representaciones en complemento

- Representación en complemento a 2: usada por la práctica totalidad de computadores actuales para números enteros.

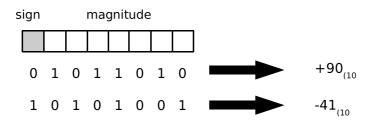

# Representación signo-magnitud (s-m) con n bits

- Emplea un bit para el signo y el resto para la magnitud:

- Signo: 0(+), 1(-)

- Números representables: 2<sup>n</sup>-1

- Dos representaciones del "0": 00000000, 10000000

$$-(2^{n-1}-1) \le x \le 2^{n-1}-1$$

Departamento de Tecnología Electrónica - Universidad de Sevilla

# Representación signo-magnitud con n bits

- Ventajas

- Fácil de entender

- Fácil de obtener el opuesto

- Inconvenientes

- Para operar con números en s-m hay que determinar previamente su signo.

- La operación a realizar depende del signo de los operandos.

- Se requieren circuitos complejos para operar con número representados en s-m.

- Usos

- No usado en la práctica para números enteros.

- Un concepto similar se usa en la representación de números reales (punto flotante).

### Representación en exceso o sesgada

- Dado un número x, y un exceso e, la representación en exceso-e con n bits consiste en representar x mediante la codificación en binario natural de la magnitud x+e con n bits.

- $0 \le x + e < 2^{n}$   $e = 2^{n-1}$   $0 \le x + 2^{n-1} < 2^{n}$

- Para que la representación sea correcta, el resultado debe ser un entero positivo representable con n bits.

- $-2^{n-1} \le x < 2^{n-1}$

- Con n bits, un valor frecuente para el exceso es  $2^{n-1}$ .

- Aproximadamente mismo número de positivos y negativos

- El primer bit de la palabra indica el signo: 0negativo, 1-positivo.

- Ej: exceso- $2^{n-1}$  (n=8  $\rightarrow$   $2^{n-1}$ =128)

- $-35_{(10)} \rightarrow -35 + 128 = 93 = 01011101_{\text{exc-}128}$

Departamento de Tecnología Electrónica - Universidad de Sevilla

### Representación en exceso o sesgada

- Ventajas

- Fácil de convertir entre el número y la representación

- Inconvenientes

- No es fácil obtener el opuesto

- Se necesitan circuitos complejos para operar con números en rep. en exceso.

- Ejemplo de uso

- Exponente en la representación de números reales (punto flotante)

| Binario | Positivo | Exceso-8 |

|---------|----------|----------|

| 0000    | 0        | -8       |

| 0001    | 1        | -7       |

| 0010    | 2        | -6       |

| 0011    | 3        | -5       |

| 0100    | 4        | -4       |

| 0101    | 5        | -3       |

| 0110    | 6        | -2       |

| 0111    | 7        | -1       |

| 1000    | 8        | 0        |

| 1001    | 9        | 1        |

| 1010    | 10       | 2        |

| 1011    | 11       | 3        |

| 1100    | 12       | 4        |

| 1101    | 13       | 5        |

| 1110    | 14       | 6        |

| 1111    | 15       | 7        |

# Representaciones en complemento con n bits

- Las representaciones en complemento usan una operación de transformación (complemento) para representar los números negativos.

- La transformación se construye de forma que el bit más significativo (msb) sea 0 para positivos y 1 para negativos.

- Representación de números positivos:

- Se representan en binario natural

- El bit más significativo debe ser 0

- Representación de números negativos

- Se representan haciendo la operación "complemento" al opuesto (positivo)

- Cambio de signo

- La representación del opuesto de un número se obtiene haciendo la operación "complemento" a la representación del número.

- Operaciones complemento típicas

- Complemento a dos, complemento a uno, complemento a la base,

Departamento de Tecnología Electrónica - Universidad de Sevilla

### Representación en complemento a 1

- Emplea la operación de complemento a 1 (complementar todos los bits).

- El primer bit indica el signo.

- Hace años la emplearon algunos ordenadores, pero hoy está en desuso.

- Ventajas

- Facilidad de obtener el opuesto

- Inconvenientes

- Dos representaciones del cero

- Circuitos más complejos

| Binario | Positivo | RC1 |

|---------|----------|-----|

| 0000    | 0        | 0   |

| 0001    | 1        | 1   |

| 0010    | 2        | 2   |

| 0011    | 3        | 3   |

| 0100    | 4        | 4   |

| 0101    | 5        | 5   |

| 0110    | 6        | 6   |

| 0111    | 7        | 7   |

| 1000    | 8        | -7  |

| 1001    | 9        | -6  |

| 1010    | 10       | -5  |

| 1011    | 11       | -4  |

| 1100    | 12       | -3  |

| 1101    | 13       | -2  |

| 1110    | 14       | -1  |

| 1111    | 15       | 0   |

$$-(2^{n-1}-1) \le x \le 2^{n-1}-1$$

### Complemento a 1

- Definición (Operación Complemento a 1 con n bits): Dado un entero positivo x < 2<sup>n</sup>, se define el complemento a 1 con n bits de x, C1<sub>n</sub>(x), a la magnitud que resulta de complementar todos los bits de x expresado en base 2.

- Definición (Representación en Complemento a 1 con n bits -RC1n-): Dado un entero x tal que -2<sup>n-1</sup> < x < 2<sup>n-1</sup>, la representación en complemento a 1 de x con n bits (RC1n) es una palabra binaria de n bits de magnitud RC1<sub>n</sub>(x) tal que:

```

- RC1_n(x) = x, si 0 \le x < 2^{n-1}

- RC1_n(x) = C1_n(-x), si -2^{n-1} < x < 0

```

• Definición 2 (Representabilidad en complemento a 1): Si  $x<-(2^{n-1}-1)$  o  $x>2^{n-1}-1$  se dice que x no es representable en complemento a 1 con n bits.

Departamento de Tecnología Electrónica - Universidad de Sevilla

### Representación en complemento a 2

- Aprovecha la "forma" de sumar del sumador de magnitudes

- $s = (a+b) \mod 2^n$

- Se puede sumar un número negativo utilizando uno positivo:

- -5+(-3)=2

- $(5 + 13) \mod 16 = 18 \mod 16 = 2$

- En general, si x<0, basta sustituirlo por x+2<sup>n</sup>

- Se imponen límites para distinguir positivos de negativos

- 0 ...  $2^{n-1}$ -1 → positivos (msb=0) -  $2^{n-1}$ ...  $2^n$ -1 → negativos (msb=1)

- Funciona para todos las combinaciones de a y b, salvo idesbordamiento!

| Binario | Positivo | Negativo | RC2 |

|---------|----------|----------|-----|

| 0000    | 0        | 0        | 0   |

| 0001    | 1        | -15      | 1   |

| 0010    | 2        | -14      | 2   |

| 0011    | 3        | -13      | 3   |

| 0100    | 4        | -12      | 4   |

| 0101    | 5        | -11      | 5   |

| 0110    | 6        | -10      | 6   |

| 0111    | 7        | -9       | 7   |

| 1000    | 8        | -8       | -8  |

| 1001    | 9        | -7       | -7  |

| 1010    | 10       | -6       | -6  |

| 1011    | 11       | -5       | -5  |

| 1100    | 12       | -4       | -4  |

| 1101    | 13       | -3       | -3  |

| 1110    | 14       | -2       | -2  |

| 1111    | 15       | -1       | -1  |

### Complemento a 2

- Definición (Representación en Complemento a 2 con n bits -RC2n-): Dado un entero x tal que -2<sup>n-1</sup> ≤ x < 2<sup>n-1</sup>, la representación en complemento a 2 de x con n bits (RC2n) es una palabra binaria de n bits de magnitud RC2<sub>n</sub>(x) tal que:

- $RC2_n(x) = x$ , si  $0 \le x < 2^{n-1}$ -  $RC2_n(x) = 2^n + x$ , si  $-2^{n-1} \le x < 0$

- Definición (Representabilidad en complemento a 2): Si  $x<-2^{n-1}$  o  $x>2^{n-1}-1$  se dice que x no es representable en complemento a 2 con n bits.

- Definición (Operación Complemento a 2 con n bits): Dado un entero positivo x < 2<sup>n</sup>, se define el complemento a 2 con n bits de x, C2<sub>n</sub>(x), como:

$$- C2_n(x) = 2^n - x$$

- Representación en Complemento a 2 reformulada:

- $RC2_n(x) = x$ , si  $0 \le x < 2^{n-1}$

- $RC2_n(x) = C2_n(-x)$ , si  $-2^{n-1} \le x < 0$

Departamento de Tecnología Electrónica - Universidad de Sevilla

### Complemento a 2

- Teorema (Bit de signo): Si x es representable en complemento a 2 con n bits, el bit más significativo de la representación en complemento a 2 de x es 0 si x ≥ 0, y 1 si x < 0.</li>

- Teorema (Cálculo del opuesto): Dado un entero x representable en complemento a 2 con n bits, la magnitud de la RC2n de -x es el complemento a 2 de la magnitud de la RC2n de x, siempre que -x sea representable en complemento a 2, esto es:

- $RC2_n(-x) = C2_n(RC2_n(x))$

- En RC2n el opuesto se calcula aplicando la operación complemento a 2 sobre la representación.

#### Complemento a 2

- Teorema (Regla de la suma): Dados dos enteros a y b tales que a, b y a+b son representables en complemento a 2 con n bits, la magnitud de la RC2n de a+b se puede calcular como:

- $RC2_n(a+b) = [RC2_n(a) + RC2_n(b)] \mod 2^n$

Esto es: la RC2n de a+b se obtiene sumando las RC2n de a y de b y despreciando posibles bits de acarreo.

Corolario: Un sumador de magnitudes de n bits cuyos operandos son las RC2n de a y b produce la RC2n de a+b, siempre que ésta sea representable con n bits.

Departamento de Tecnología Electrónica - Universidad de Sevilla

### Complemento a 2

- Definición (Desbordamiento en complemento a 2): Dados dos enteros a y b representables en complemento a 2 con n bits, se dice que la suma de a y b produce desbordamiento en complemento a 2 con n bits si a+b no es representable en complemento a 2 con n bits.

- Corolario (Regla del desbordamiento): Dados dos enteros a y b representables en complemento a 2 con n bits, la suma a+b es representable en complemento a 2 con n bits si y sólo si:

- a y b tienen distinto signo o al menos uno de ellos es cero, o bien

- a y b tienen el mismo signo y el resultado de la suma de las RC2n de a y b, módulo 2<sup>n</sup>, tiene el mismo bit de signo que las RC2n de a y b.

# Complemento a 2 Suma y desbordamiento

$$1100 = -4$$

$0101 = +5$   $1001 = -7$   $1111 = -1$   $0100 = +4$   $1010 = -6$   $--- 1001 = -7$   $10011 = +3$

Departamento de Tecnología Electrónica - Universidad de Sevilla

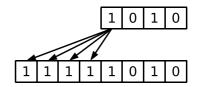

# Complemento a 2 Relación con el complemento a 1

- Teorema: el complemento a 1 con n bits de x puede calcularse como:

- $-C1_n(x) = 2^n x 1$

- Relación:

- $C1_n(x) = C2_n(x) 1$

- $C2_n(x) = C1_n(x) + 1$

- Regla 1

- El C2<sub>n</sub>(x) puede obtenerse complementando todos los bits de x y sumando 1 al resultado.

- Regla 2

- El C2<sub>n</sub>(x) puede obtenerse conservando todos los bits de x que sean '0' comenzando por el menos significativo hasta el primer '1' inclusive y complementando el resto de bits.

### Complemento a 2 Ejemplos

- Ejemplo 1: representar las siguientes cantidades en C2 con 8 bits.

- 32, -13, 115, -140, 128, -128

- Ejemplo 2: obtener el número mínimo de bits necesarios para representar las cantidades anteriores en C2.

- Ejemplo 3: calcular el valor decimal de las siguientes representaciones en C2.

- 01001100, 11110000

Departamento de Tecnología Electrónica - Universidad de Sevilla

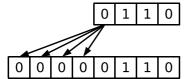

# Complemento a 2 Extensión del signo

Teorema (Extensión del signo en complemento a 2): Sea x un entero representable en complemento a 2 y RC2<sub>n</sub>(x) la magnitud de su representación en complemento a 2 con n bits y s el bit de signo de dicha magnitud. Se cumple que:

$$- RC2_{n+1}(x) = s 2^n + RC2_n(x)$$

Esto es, la representación en complemento a 2 de  $\times$  con n+1 bits coincide con la representación con n bits añadiendo un bit de signo igual al bit de signo de la representación con n bits.

Corolario: Un entero x representable en complemento a 2 con n bits será representable en complemento a 2 con n-1 bits si los dos bits más significativos de RC2n(x) son iguales (el signo no cambia al reducir el número de bits).

# Complemento a 2 C2 como código pesado

Teorema: Sea x un entero representable en complemento a 2 con n bits, RC2<sub>n</sub>(x) la magnitud de su representación en complemento a 2 con n bits formada por las cifras binarias {x<sub>0</sub>,x<sub>1</sub>,...,x<sub>n-1</sub>}. Se tiene que:

$$X = -2^{n-1}X_{n-1} + 2^{n-2}X_{n-2} + ... + 2X_1 + X_0$$

| -2 <sup>7</sup> |    |    |    |   |   |   |   |         |     |

|-----------------|----|----|----|---|---|---|---|---------|-----|

| -128            | 64 | 32 | 16 | 8 | 4 | 2 | 1 |         |     |

| 1               | 0  | 1  | 1  | 0 | 1 | 1 | 0 | <b></b> | -74 |

| 1               | 1  | 1  | 1  | 1 | 1 | 1 | 0 | <b></b> | -2  |

| 0               | 1  | 0  | 0  | 0 | 0 | 0 | 1 | <b></b> | 65  |

Departamento de Tecnología Electrónica - Universidad de Sevilla

# Resumen de números con signo

| Х  | S-M       | Exc-2 <sup>n-1</sup> | RC1       | RC2  |

|----|-----------|----------------------|-----------|------|

| -8 | -         | 0000                 | -         | 1000 |

| -7 | 1111      | 0001                 | 1000      | 1001 |

| -6 | 1110      | 0010                 | 1001      | 1010 |

| -5 | 1101      | 0011                 | 1010      | 1011 |

| -4 | 1100      | 0100                 | 1011      | 1100 |

| -3 | 1011      | 0101                 | 1100      | 1101 |

| -2 | 1010      | 0110                 | 1101      | 1110 |

| -1 | 1001      | 0111                 | 1110      | 1111 |

| 0  | 0000/1000 | 1000                 | 0000/1111 | 0000 |

| 1  | 0001      | 1001                 | 0001      | 0001 |

| 2  | 0010      | 1010                 | 0010      | 0010 |

| 3  | 0011      | 1011                 | 0011      | 0011 |

| 4  | 0100      | 1100                 | 0100      | 0100 |

| 5  | 0101      | 1101                 | 0101      | 0101 |

| 6  | 0110      | 1110                 | 0110      | 0110 |

| 7  | 0111      | 1111                 | 0111      | 0111 |

#### **Contenidos**

- Introducción

- · Aritmética binaria

- · Circuitos sumadores básicos

- · Sumador de magnitudes

- Números binarios con signo

- · Sumador con signo. Desbordamiento

- Sumador/restador

- ALU

Departamento de Tecnología Electrónica - Universidad de Sevilla

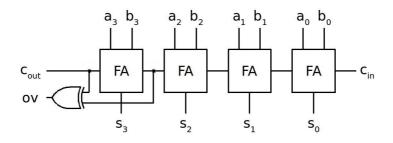

# Sumador con signo: desbordamiento

- · Mismo sumador que para magnitudes.

- El bit de acarreo NO indica desbordamiento en C2.

- Se necesita un indicador de desbordamiento para la suma en C2. Basado en la regla del desbordamiento.

- Signo de operandos y resultado

### Sumador con signo: desbordamiento

Departamento de Tecnología Electrónica - Universidad de Sevilla

Departamento de Tecnología Electrónica - Universidad de Sevilla

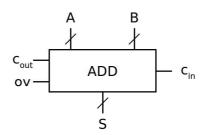

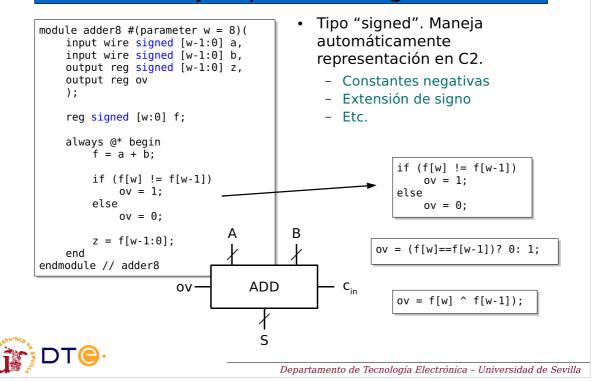

# Sumador con/sin signo Ejemplos Verilog

```

В

Α

Usando sumadores completos

module adder8 fa(

input [7:0] a, input [7:0] b,

\mathbf{C}_{\mathrm{in}}

ADD

ov-

input cin,

output [7:0] s,

1

output cout, ov

S

Usando operadores aritméticos

// auxiliary signal

wire [7:1] c;

module adder8(

input [7:0] a,

fa fa0 (a[0], b[0], cin, s[0], c[1]);

input [7:0] b,

fa fal (a[1], b[1], c[1], s[1], c[2]);

fa fa2 (a[2], b[2], c[2], s[2], c[3]);

fa fa3 (a[3], b[3], c[3], s[3], c[4]);

input cin,

output [7:0] s,

output cout, ov

fa fa4 (a[4], b[4], c[4], s[4], c[5]);

fa fa5 (a[5], b[5], c[5], s[5], c[6]);

fa fa6 (a[6], b[6], c[6], s[6], c[7]);

fa fa7 (a[7], b[7], c[7], s[7], cout);

assign {cout, s} = a+b+cin;

assign ov = \sim a[7] \& \sim b[7] \& s[7]

assign ov = c[7] ^ cout;

| a[7] & b[7] & ~s[7];

endmodule // adder8 fa

endmodule // adder8

```

# Sumador con signo Ejemplos Verilog

#### **Contenidos**

- Introducción

- · Aritmética binaria

- Circuitos sumadores básicos

- · Sumador de magnitudes

- · Números binarios con signo

- Sumador con signo. Desbordamiento

- Sumador/restador

- ALU

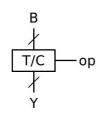

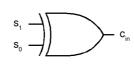

# Sumador/restador Bloque transfiere/complementa

$$Y = \overline{B} = C1_n(B) = 2^n-B-1 = C2_n(B)-1$$

Si B=RC2<sub>n</sub>(b), entonces:

$$Y+1 = C2_n(B) = RC2_n(-b)$$

Departamento de Tecnología Electrónica - Universidad de Sevilla

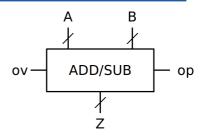

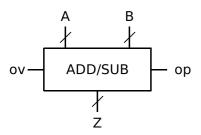

# Sumador/restador

- Sumador/restador en complemento a 2

- A=RC2n(a), B=RC2n(b), Z=RC2n(z)

- ov: salida de desbordamiento (z no representable en C2)

| ор | Z     | Z       |

|----|-------|---------|

| 0  | a + b | A + B   |

| 1  | a - b | A+C2(B) |

| ор | Y              | C <sub>in</sub> | Z              | Z     |

|----|----------------|-----------------|----------------|-------|

| 0  | В              | 0               | A + B          | a + b |

| 1  | $\overline{B}$ | 1               | A+ <u>B</u> +1 | a - b |

$$\overline{B}+1 = C1_n(B)+1 = C2_n(B)$$

# Sumador/restador Descripción Verilog

```

module addsub \#(parameter w = 8)(

input wire signed [w-1:0] a,

input wire signed [w-1:0] b,

input wire op,

output reg signed [w-1:0] z,

output reg ov

);

reg signed [w:0] f;

always @* begin

case (op)

0:

f = a + b;

default:

f = a - b;

endcase

ov = f[w] ^ f[w-1]);

z = f[w-1:0];

end

endmodule // addsub

```

Departamento de Tecnología Electrónica - Universidad de Sevilla

#### **Contenidos**

- Introducción

- · Aritmética binaria

- Circuitos sumadores básicos

- · Sumador de magnitudes

- · Números binarios con signo

- Sumador con signo. Desbordamiento

- Sumador/restador

- · ALU

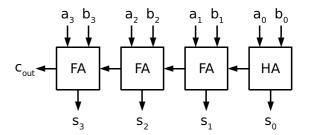

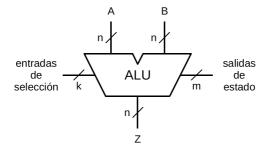

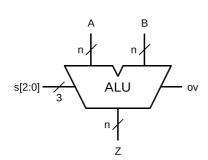

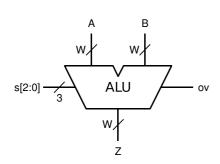

#### **ALU**

- Conjunto de operaciones de procesado de datos agrupadas en un mismo dispositivo

- Operaciones lógicas

- Operaciones aritméticas

- Uno de los componentes más importantes del computador

Departamento de Tecnología Electrónica - Universidad de Sevilla

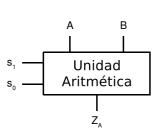

# ALU de ejemplo

- Unidad Lógico-Aritmética en complemento a 2

- A = RC2n(a), B = RC2n(b), Z = RC2n(z)

- ov: salida de desbordamiento (z no representable en C2)

| $S_2S_1S_0$ | Z     | Z                   |                                 |

|-------------|-------|---------------------|---------------------------------|

| 000         | a + b | A + B               | )                               |

| 001         | a - b | A+C2(B)             | Aritméticas ( $s_2=0$ )         |

| 010         | a + 1 | A + 1               | Antimeticas (s <sub>2</sub> =0) |

| 011         | a - 1 | A+2 <sup>n</sup> -1 | J                               |

| 100         | A AI  | ND B                |                                 |

| 101         | АО    | R B                 | Lógicas (s,=1)                  |

| 110         | A XC  | OR B                | Logicas (S <sub>2</sub> -1)     |

| 111         | NO    | ТА                  | J                               |

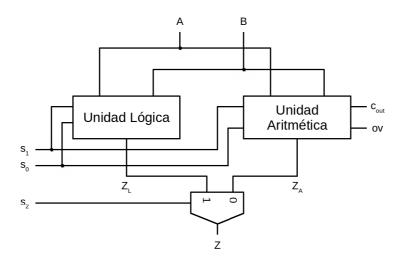

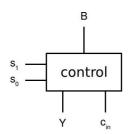

# ALU Estrategia de diseño

- iDivide y vencerás! (otra vez)

- Diseñar una unidad lógica y una unidad aritmética independientes controladas por s<sub>2</sub> (¿multiplexor?)

- Unidad lógica

- Seleccionar la operación adecuada con  $s_1$  y  $s_0$  (¿multiplexor?)

- · Unidad aritmética

- Usar un sumador de magnitudes como base.

- Calcular las entradas del sumador (B y Cin) para obtener el resultado deseado.

- Seleccionar los valores apropiados de B y Cin con s<sub>1</sub> y s<sub>0</sub>

(¿multiplexor?)

Departamento de Tecnología Electrónica - Universidad de Sevilla

#### ALU Diseño

Departamento de Tecnología Electrónica - Universidad de Sevilla

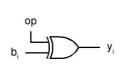

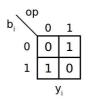

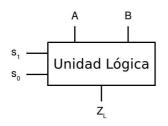

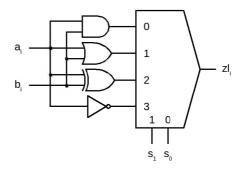

# ALU Diseño de la unidad lógica

| S <sub>1</sub> S <sub>0</sub> | zl                  | zl <sub>i</sub>                   |

|-------------------------------|---------------------|-----------------------------------|

| 00                            | a AND b             | a <sub>i</sub> AND b <sub>i</sub> |

| 01                            | a OR $\overline{b}$ | $a_i$ OR $\overline{b_i}$         |

| 10                            | a XOR b             | a <sub>i</sub> XOR b <sub>i</sub> |

| 11                            | NOT a               | NOT a <sub>i</sub>                |

Departamento de Tecnología Electrónica - Universidad de Sevilla

В

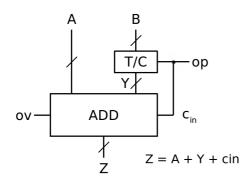

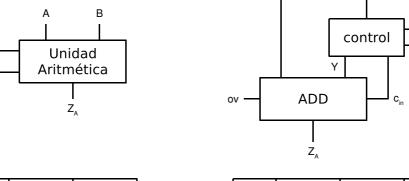

# **ALU** Diseño de la unidad aritmética

| $S_1S_0$ | Z <sub>A</sub> | $Z_A$                  |

|----------|----------------|------------------------|

| 00       | a + b          | A + B                  |

| 01       | a – b          | $A + \overline{B} + 1$ |

| 10       | a + 1          | A + 1                  |

| 11       | a - 1          | A + 2 <sup>n</sup> -1  |

| $Z_A = A + Y + C_{in}$ |

|------------------------|

|                        |

| <u> </u>               |

| $S_1S_0$ | Y                 | y <sub>i</sub>     | C <sub>in</sub> |

|----------|-------------------|--------------------|-----------------|

| 00       | В                 | b <sub>i</sub>     | 0               |

| 01       | B                 | $\overline{b}_{i}$ | 1               |

| 10       | 0                 | 0                  | 1               |

| 11       | 2 <sup>n</sup> -1 | 1                  | 0               |

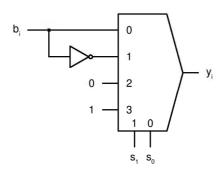

# ALU Diseño de la unidad aritmética

| S <sub>1</sub> S <sub>0</sub> | у                 | y <sub>i</sub>     | C <sub>in</sub> |

|-------------------------------|-------------------|--------------------|-----------------|

| 00                            | b                 | b <sub>i</sub>     | 0               |

| 01                            | b                 | $\overline{b}_{i}$ | 1               |

| 10                            | 0                 | 0                  | 1               |

| 11                            | 2 <sup>n</sup> -1 | 1                  | 0               |

Departamento de Tecnología Electrónica - Universidad de Sevilla

# ALU Descripción Verilog

```

module alu #(parameter w = 8)(

input signed [w-1:0] a,

input signed [w-1:0] b,

input [2:0] s,

output reg signed [w-1:0] z,

output reg ov

);

reg signed [w:0] f;

```

```

always @* begin

ov = 0;

if (f[2] == 0) begin // Arithmetic

case (f[1:0])

2'b00: f = a + b;

2'b01: f = a - b;

2'b10: f = a + 1;

2'b11: f = a - 1;

2'b11:

endcase

ov = (f[w] == f[w-1])? 0: 1;

z = f[w-1:0];

end else

// Logic

case (s[1:0])

2'b00: z = a & b;

2'b01: z = a | b;

2'b10: z = a ^ b;

2'b11: z = ~a;

endcase

end // always

endmodule // alu

```