|    | _           | _   | _                            | _     |       |

|----|-------------|-----|------------------------------|-------|-------|

|    | C C T C     |     | $\mathbf{I} \sim \mathbf{A}$ | DICI. | T A I |

| ᄄᆫ | <b>ECTF</b> | KUN | ILA                          | DIGI  | IAL   |

### CONTROL 2. Curso 2018-2019

| Apellidos:SOLUCIÓN | 1_ | 2 |

|--------------------|----|---|

| ApellidosSOLUCION  |    |   |

| Nombre:            |    |   |

### Duración 2:00 h.

- **1.-** [2 Puntos] Tipos de memoria según:

- a) Modo de acceso.

- b) Permanencia de la información.

## **SOLUCIÓN**

- a) En este apartado hay que explicar los siguientes modos de acceso:

- Aleatorio

- Secuencial

- LIFO

- FIFO

- Por contenido

- b) En este apartado hay que explicar las siguientes formas de permanencia:

- Permanente

- No volátil

- Volátil

- · Con refresco

- **2.-** [2 Puntos] Arquitecturas de referencia para computadores: descripción y comparación.

# **SOLUCIÓN**

En esta pregunta hay que describir las caracteríticas de ambas arquitecturas con todos sus componentes (CPU, E/S, buses y memoria) y después explicar las diferencias y hacer una comparación de ventajas e inconvenientes de la una frente a la otra (complejidad/precio, rendimiento, flexibilidad de anchura de buses y flexibilidad del uso de la memoria).

| Apellidos:SOLUCIÓN | 3 | 4 |

|--------------------|---|---|

| ApelliuosOCCOOlON  |   |   |

| Nombre:            |   | İ |

**3.-** [3 puntos] Se desea diseñar un circuito que controle la escritura de una memoria RAM de 8 palabras de 16 bits. El circuito tiene una entrada de 8 bits por el que va recibiendo los bytes a escribir en la memoria. Una señal Xs iniciará el proceso de escritura. Tras la activación, en el siguiente ciclo de reloj se recibe el byte a escribir en la parte menos significativa de la fila 0 de la memoria. El segundo byte recibido hay que escribirlo en la parte más significativa de la fila 0. Después se reciben los byes de la fila 1 (de la misma forma), después los de la fila 2, y así sucesivamente hasta completar la memoria. Todos los bytes se reciben de forma consecutiva (en 16 ciclos de reloj).

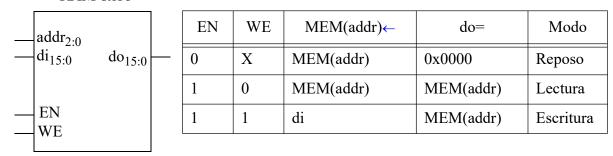

### **RAM 8x16**

- **a)** Proponga una unidad de datos lo más sencilla posible. Describa a nivel RT los componentes que necesite.

- **b)** Diseñe las cartas ASM de las Unidades de Datos y de Control de un controlador que permita realizar esta operación.

- c) Realice una implementación de la UC usando la técnica de un biestable por estado.

# **SOLUCIÓN**

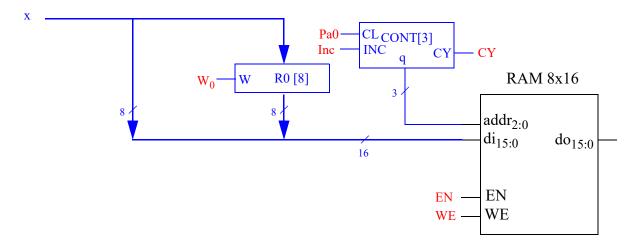

a) Para la unidad de datos se va a plantear un registro R0 donde almacenar el byte bajo de cada palabra a escribir. Este registro tendrá entradas y salidas separadas. No necesita alta impedancia porque los 16 bits del bus de datos de la RAM irán en paralelo. Además se necesita un contador módulo 8 que cuente las ocho palabras a escribir en la memoria. La salida del contador se utiliza como entrada de dirección de la memoria. El contador tendrá una entrada de puesta a cero y otra entrada de incremento, así como una salida de carry. La unidad de datos sería:

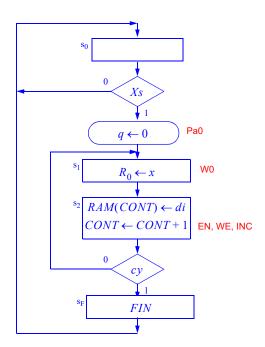

b) La unidad de datos irá almacenando en el registros R0 los bytes impares temporalmente, hasta que lleguen los pares. Cuando ocurra esto, se escribirán directamente en la RAM los

datos de 16 bytes, en los que los 8 lsb los paorta R0 y los 8 msb directamente el bus X. Así hasta escribir las ocho filas. La carta ASM de datos y control será:

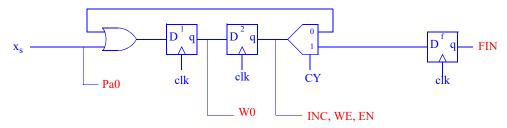

c) El circuito, con la técnica de un biestable por estado es:

- 4.- [3 puntos] Para el CS3 se quiere realizar:

- **a)** Una subrutina que haga la suma de dos datos sin signo que se encuentran almacenados en la dirección indicada por R0 y la siguiente. El resultado debe guardarse en la siguiente posición de la memoria de datos (es decir, en R0+2) si no hay desbordamiento. En caso de overflow se almacenará el valor cero.

- **b)** Se desea introducir la instrucción **MOVS Rd**, **SP**, que escribe en el registro Rd el contenido del puntero de pila. Indique qué formato de instrucción usará. ¿Es necesario modificar la unidad de datos? Justifique la respuesta. En caso afirmativo, explique dichos cambios. Indique la secuencia de microoperaciones de esta instrucción.

### **SOLUCIÓN**

a) La rutina debe copiar los datos de la memoria a dos registros, realizar la suma, comprobar el resultado y después volver a escribir los datos en la memoria. Como no es necesario mantener el valor de R0, vamos a ir incrementando el valor almacenado en ese registro.

```

; Suma dos datos en memoria

v1.0

; Las direcciones de memoria en los que están almacenados son (RO) y (RO)+1

; El resultado se deja en (r0)+2

R2, (R0) ; R2=primer dato

SUM MEM: LD

ADDI

RO, 1 ; Avanzar puntero

R3, (R0) ;R3=segundo dato

LD

R0, 1

ADDT

;Avanzar puntero

R3, R2

ADD

;R3=R3+R2

```

```

BRCS DESB ;Se debordó? Sí, procesar error

JMP SUMFIN ;...no, guardar resultado y salir

DESB: LDI R3, 0 ;R:=0 significa error

SUMFIN: ST (R0), R3 ;Resultado a memoria

RET

```

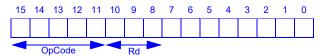

b) Formato de instrucción: El único parámetro es el registro en el que almacenar el contenido del registro de pila. El valor de este registro debe estar en los bits 10 a 8 de la instrucción. El formato de instrucción puede ser el tipo A (de acceso a registros).

Como sólo se requiere escribir el contenido del registro SP en el banco de registros, el acceso se puede hacer utilizando el bus compartido, con lo que no es necesario modificar la arquitectura del procesador.

Respecto a la secuencia de microinstrucciones sólo es necesaria una: Rd <- SP.