|    |     | ,   |    |        |   |     |     |  |

|----|-----|-----|----|--------|---|-----|-----|--|

|    | EC1 | FD  | M  | $\sim$ |   | OI. |     |  |

| ᆮᆫ | .EG | IRL | NI | ILA    | ப | GI  | IAL |  |

FINAL Segunda Convocatoria 2022-2023

|                                  |  | <br>3 | 4 | 5 | O |

|----------------------------------|--|-------|---|---|---|

| Apellidos: <mark>SOLUCIÓN</mark> |  |       |   |   |   |

|                                  |  |       |   |   |   |

| Nombre:                          |  |       |   |   |   |

## TEORÍA (Cada pregunta vale 1 punto)

- **1.-** Defina breve y claramente los siguientes términos:

- I<sub>OH</sub>

- Azar

- · Codificador de prioridad

- Contador incompleto

- Full adder

- Microoperación

- Arquitectura Harvard

- · Direccionamiento absoluto

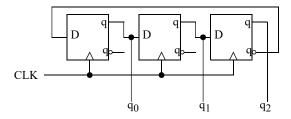

- **2.-** Analice el circuito de la figura e indique qué hace. Suponga que inicialmente los biestables tienen el estado 0.

**SOLUCIÓN**

## Análisis 1:

Al tratarse de un circuito tan sencillo, podemos hacer un análisis modular. La evolución de los estados  $(q_{2:0})$  sería: 000, 001, 011, 111, 110, 100 y vuelta a empezar. Es una especie de registro de desplazamiento circular en el que la realimentación se realiza con la salida invertida. Lo que se obtiene es un contador módulo 6 que se llama contador Jhonson.

Análisis 2: aplicando la metodología genérica vista en clase, tenemos

• Ecuaciones de Excitación/Salida:

$$D_0 = q_2$$

$$D_1 = q_0$$

$$D_2 = q_1$$

• Tabla de Excitación/Salida:

|            |          | 1 | 2 | 3 | 4 | 5 | Ь |

|------------|----------|---|---|---|---|---|---|

| Apellidos: | SOLUCIÓN |   |   |   |   |   |   |

| Nombre:    |          |   |   |   |   |   |   |

Tabla de Transición/Salida:

| $q_0$ $q_2$ $q_0$ | 1 00      | 01  | 11  | 10  |  |  |  |

|-------------------|-----------|-----|-----|-----|--|--|--|

| 0                 | 001       | 101 | 100 | 000 |  |  |  |

| 1                 | 011       | 111 | 110 | 010 |  |  |  |

|                   | $Q_{2:0}$ |     |     |     |  |  |  |

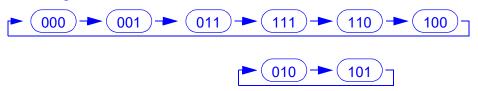

• Diagrama de Estados/Salida:

Se observa que salen dos ciclos de estados. Uno de 6 y otro de 2. Para el valor inicial que nos dan, 000, sería de aplicación el primer ciclo.

- 3.- Jerarquía de memorias de un computador. En qué consiste y para qué sirve.

- **4.-** Escriba la subrutina Ca1 en ensamblador del CS3 que recibe un número de 8 bits en R0 y deja en R1 su complemento a 1.

### **SOLUCIÓN**

#### PROBLEMAS (Cada pregunta vale 3 puntos)

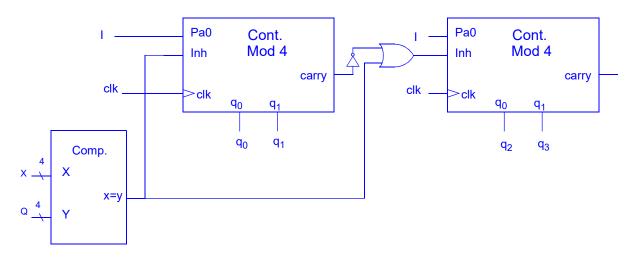

1.- Se desea diseñar un contador que cuente de forma ascendente hasta un cierto valor. Este valor estará fijado por una entrada de 4 bits (X, x<sub>3</sub>x<sub>2</sub>x<sub>1</sub>x<sub>0</sub>). La puesta a '1 de una entrada de inicio (I = '1') arrancará el proceso de cuenta empezando por el valor de cuenta cero. Una vez llegado al valor a contar, se deberá quedar parado en ese valor hasta que se produzca una nueva activación de la entrada de inicio (I = '1'). Dispone para realizar el circuito de contadores ascendentes módulo 4, comparadores de magnitud y puertas lógicas. Deberá definir las entradas y salidas especiales que deben tener los contadores y las características del comparador. El diseño ha de ser síncrono.

#### SOLUCIÓN

Para solucionar el problema hay que, primero construir un contador completo módulo 16 y después hacer que se pare al alcanzar la cuenta desada. Como toda la construcción es síncrona necesitaremos dos contadores módulo 4 con entrada síncrona de puesta a cero y con entrada de inhibición activa en alta. También deberán tener salida de carry.

Para conseguir que se pare al alcanzar la cuenta deseada utilizaremos el comparador de magnitud (de entradas de 4 bits) que comparará entre el dato que esté contando y el valor de cuenta. Cuando se alcance el estado de cuenta deseado se activará la entrada de inhibición de cuenta. El segundo contador se inhibirá tambien cuando el primer contador no esté en su último estado de cuenta. La entrada I irá conectada a la entrada de puesta a cero de los contadores. Con todo esto, el circuito es:

CRITERIO DE CORRECCIÓN

|            |           | 1 | 2 | 3 | 4 | 5 | 6 |

|------------|-----------|---|---|---|---|---|---|

| Apellidos: | .SOLUCIÓN |   |   |   |   |   |   |

| Nombre:    |           |   |   |   |   |   |   |

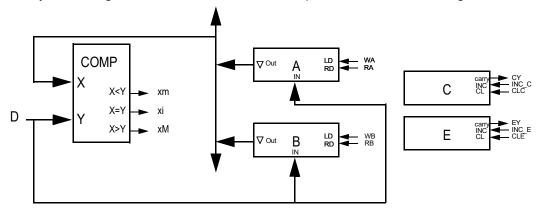

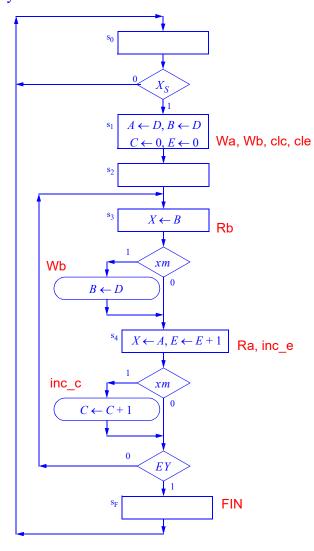

2.- Se dispone de la Unidad de Datos de la figura. Todas las señales conectadas a ambos buses son de 8 bits. El bloque "COMP" es un comparador de magnitud. Los bloques C y E son contadores módulo 16 con señal de incremento, puesta a cero y salida de carry. Los bloques A y B son registros con las características que se muestran en la figura.

Se desea realizar el siguiente comportamiento: En el ciclo de reloj siguiente a la activación de la entrada de inicio (Xs) la unidad de datos empieza a recibir por la entrada D 16 datos que contienen números sin signo. Cada dato estará en la entrada dos ciclos de reloj. El primer dato debe ser almacenado en el registro A. Una vez recibidos los 15 datos restantes, en C debe quedar el número de los datos recibidos que son menores al recibido en primer lugar (y almacenado en A) y en el registro B el menor de todos los datos siempre que sea inferior al primer dato recibido. En el caso de que todos los datos sean mayores que el primero, en B debe almacenarse el valor del primer dato (el almacenado en A).

- **a)** Describa la carta ASM de la Unidad de Datos y de la Unidad de control. Explique de forma concisa qué se hace en cada estado.

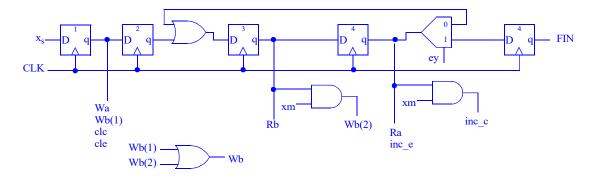

- **b)** )Dibuje el circuito que implementa la unidad de control utilizando la técnica de un biestable por estado.

#### **SOLUCIÓN**

- a) Carta ASM y descripción de cada estado.

- S0: Estado de espera de inicio.

- S1: Estado donde se recibe el primer dato (primer ciclo). Se ponen a cero los contadores y se carga el dato de entrada en A y en B.

- S2: Segundo ciclo del primer dato. Podría haberse hecho en el estado anterior, pero como se va a hacer en el resto de estados, se carga en RT el contenido de B.

- S3: Iniciamos la comparación de datos. En este primer estado comparamos el dato en la entrada con el almacenado en B para ver si es menor. Si es menor lo almacenamos en B.

- S4: Comparamos si D es menor que A. En caso afirmativo se incrementa C. Se comprueba si es el último dato. Si no se incrementa E y se vuelve a S3.

Las Cartas ASM de la UD y de la UC son:

# El circuito es:

CRITERIO DE CORRECCIÓN