## Lista de Hojas de características:

| Circuitos integrados                                | Pág. |

|-----------------------------------------------------|------|

| NAND2: 7400, 74LS00, 74S00                          | 2    |

| INV: 74LS04                                         | 8    |

| AND2: 7408, 74LS08, 74S08                           | 13   |

| NAND4: 74LS20                                       | 19   |

| OR2: 7432, 74LS32, 74S32                            | 23   |

| D PET FF: 74LS74                                    | 28   |

| JK FF: 7476, 74LS76                                 | 35   |

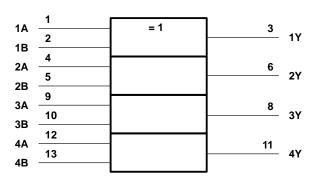

| XOR: 74LS86                                         | 42   |

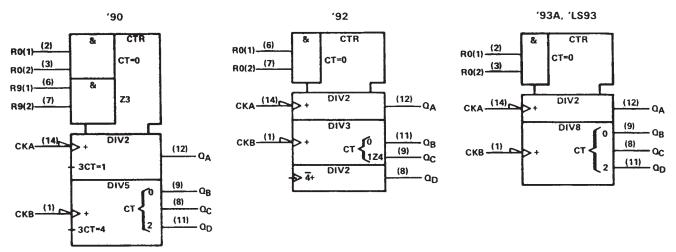

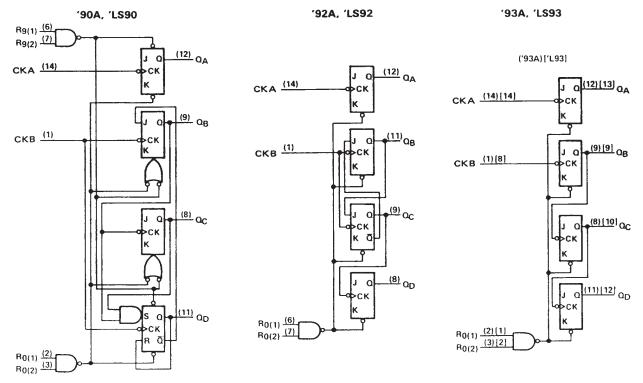

| Contador 4 bits: 74LS90, 74LS92, 74LS93             | 48   |

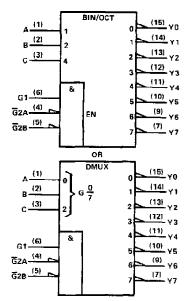

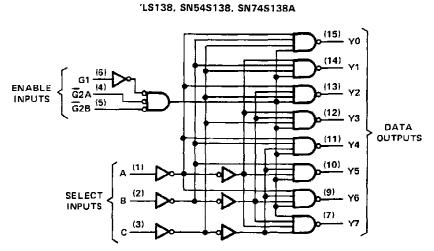

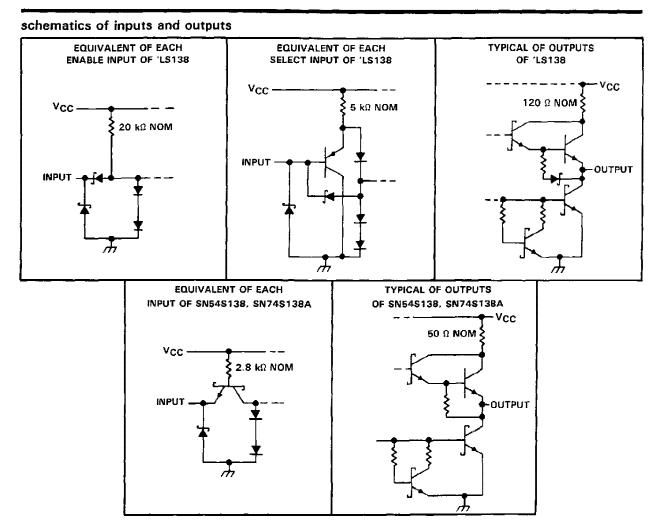

| DEC 3:8: 74LS138                                    | 60   |

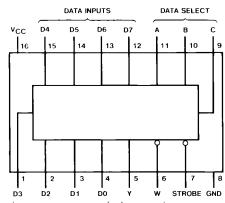

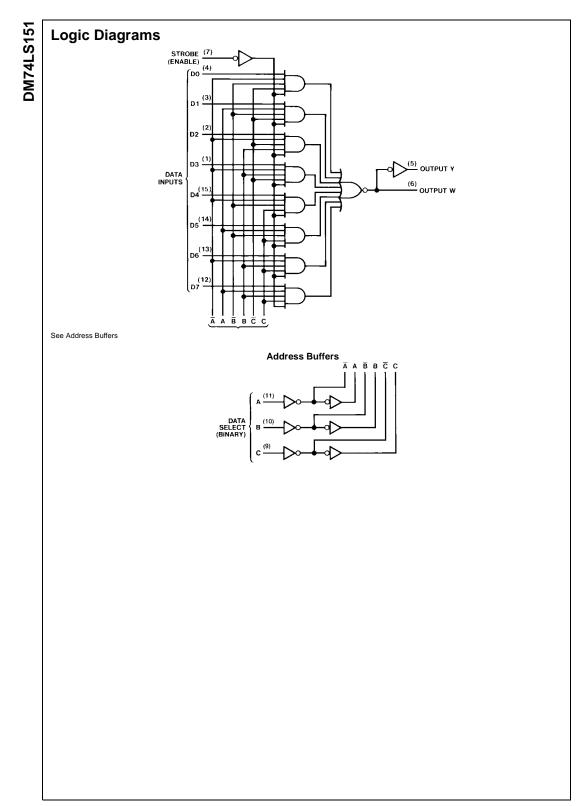

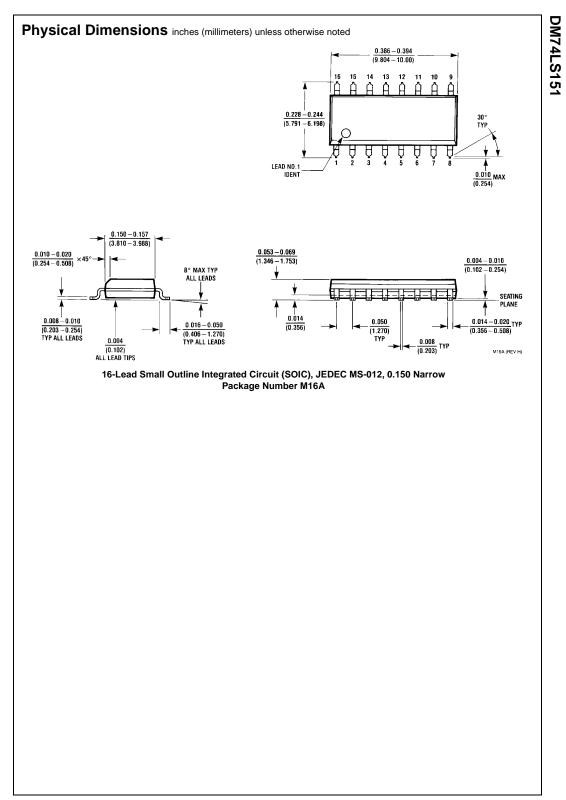

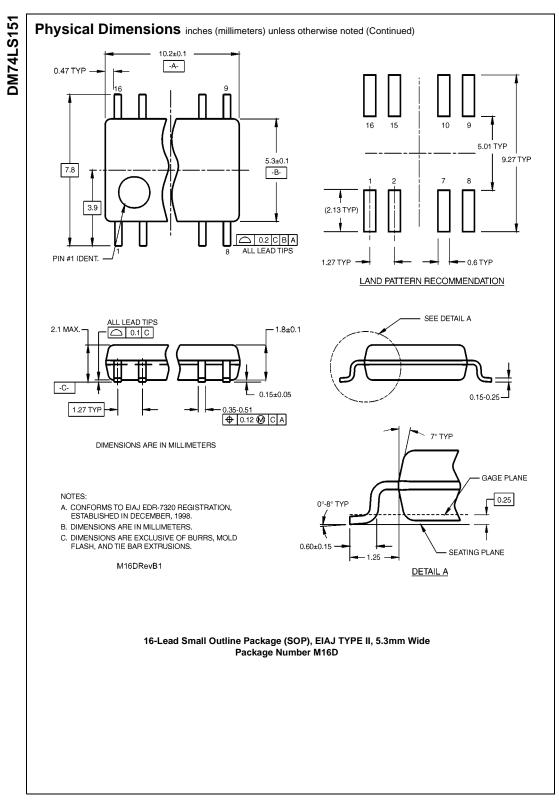

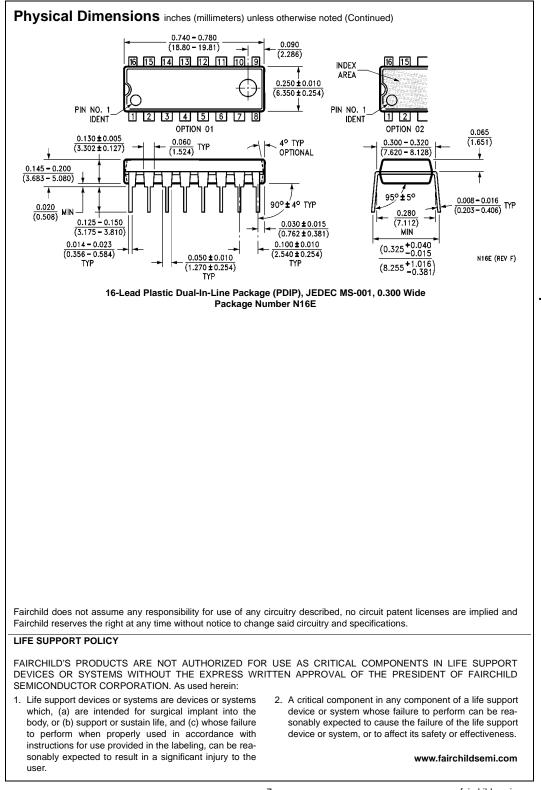

| MUX 8:1: 74LS151                                    | 68   |

| DEC 4:16: 74LS154                                   | 75   |

| Contador Sincr 4 bits: 74ALS161, 74ALS162, 74ALS163 | 80   |

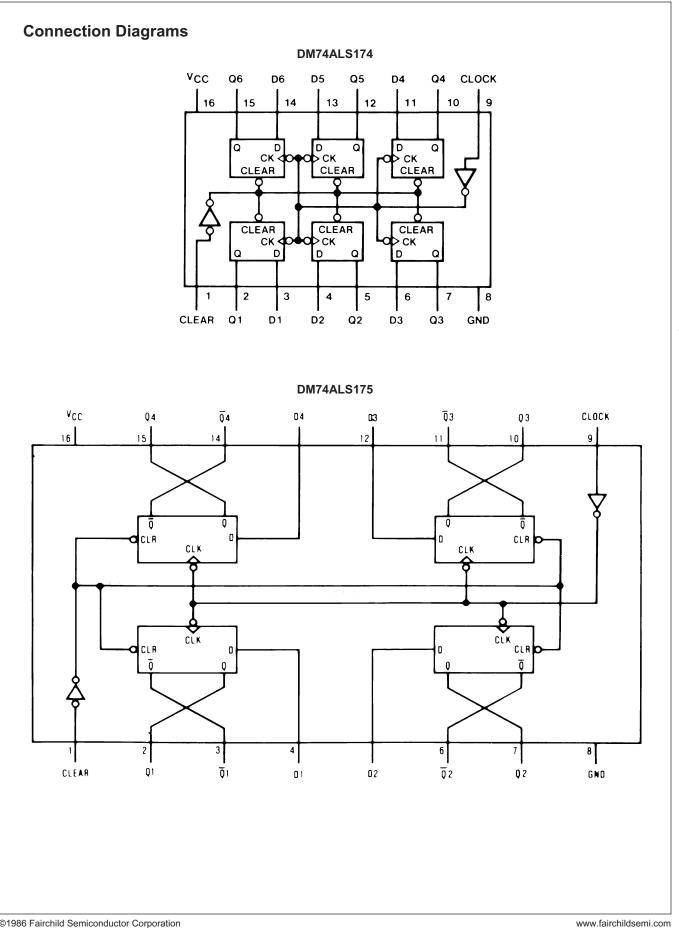

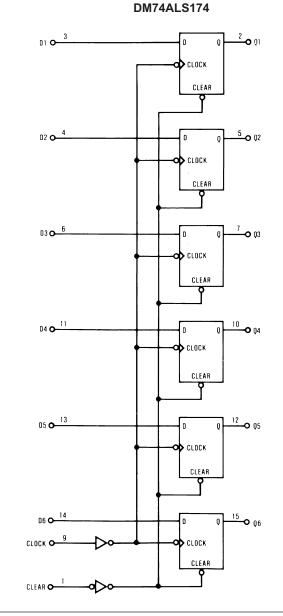

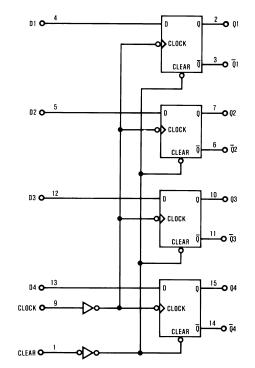

| D FF: 74ALS174, 74ALS175                            | 92   |

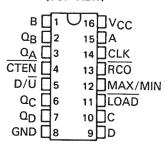

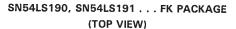

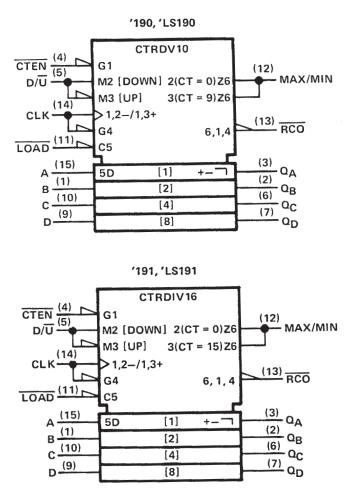

| Contador Up/Down: 74LS190, 74LS191                  | 101  |

| D FF: 74LS175 (Motorola)                            | 115  |

| Registros Parallel 4bits: 74LS195                   | 118  |

| Registros Parallel 8bits: 74LS165                   | 128  |

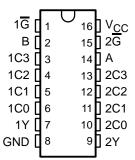

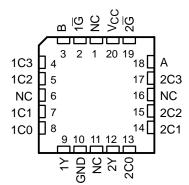

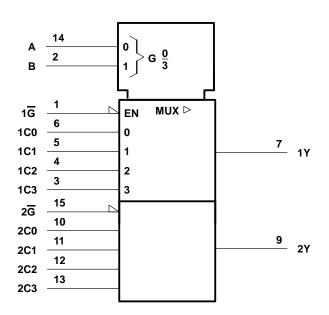

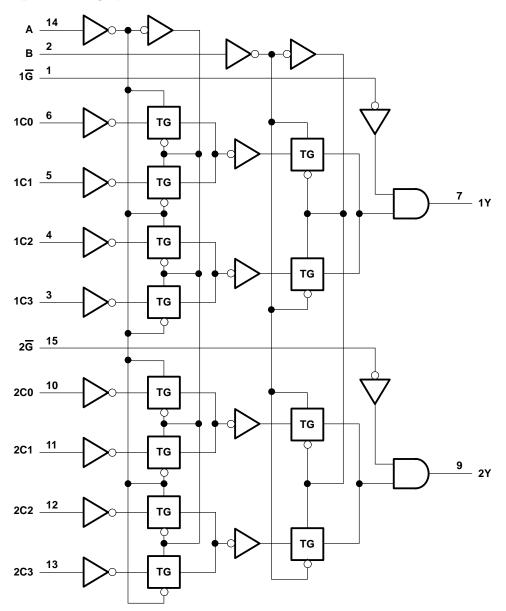

| MUX 4:1: 74HC153                                    | 139  |

|                                                     |      |

#### SN5400, SN54LS00, SN54S00 SN7400, SN74LS00, SN74S00 QUADRUPLE 2-INPUT POSITIVE-NAND GATES SDLS025 – DECEMBER 1983 – REVISED MARCH 1988

- Package Options Include Plastic "Small Outline" Packages, Ceramic Chip Carriers and Flat Packages, and Plastic and Ceramic DIPs

- Dependable Texas Instruments Quality and Reliability

#### description

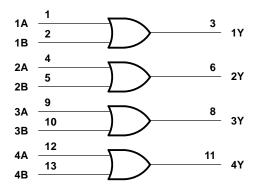

These devices contain four independent 2-input-NAND gates.

The SN5400, SN54LS00, and SN54S00 are characterized for operation over the full military temperature range of -55 °C to 125 °C. The SN7400, SN74LS00, and SN74S00 are characterized for operation from 0 °C to 70 °C.

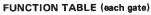

#### FUNCTION TABLE (each gate)

| INP | UTS | OUTPUT |

|-----|-----|--------|

| A   | B   | Y      |

| н   | н   | L      |

| L   | х   | н      |

| x   | L   | н      |

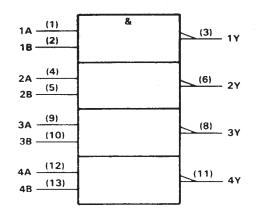

#### logic symbol<sup>†</sup>

$^{\dagger}\mbox{This symbol is in accordance with ANSI/IEEE Std. 91-1984 and IEC Publication 617-12.$

Pin numbers shown are for D, J, and N packages.

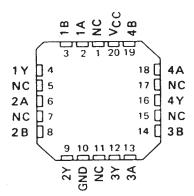

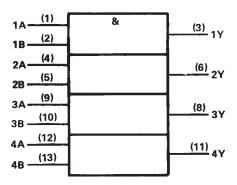

SN5400 . . . J PACKAGE SN54LS00, SN54S00 . . . J OR W PACKAGE SN7400 . . . N PACKAGE SN74LS00, SN74S00 . . . D OR N PACKAGE

#### (TOP VIEW)

| 1A  | ปา         |                 |

|-----|------------|-----------------|

| 18  |            | 13 4 B          |

| 1Y  |            | 12 4A           |

| 2A  | <b>4</b>   | 110 4Y          |

| 2B  | <b>[</b> 5 | 10 <b>] 3 B</b> |

| 2Y  | <b>G</b> e | 9 🗍 3 A         |

| GND | <b>प</b> ृ | 8 3 Y           |

|           | W PACKAGE<br>P VIEW) |

|-----------|----------------------|

| 1A [ 1    | 14 4Y                |

| 1B [ 2    | 13 4B                |

| 1Y [ 3    | 12 4A                |

| V C C [ 4 | 11 GND               |

| 2Y [ 5    | 10 3B                |

| 2A [ 6    | 9 3A                 |

| 2B [ 7    | 8 3Y                 |

#### SN54LS00, SN54S00 . . . FK PACKAGE (TOP VIEW)

NC - No internal connection

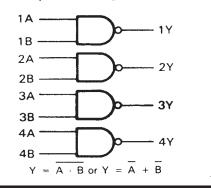

#### logic diagram (positive logic)

Copyright © 1988, Texas Instruments Incorporated

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

#### SN5400, SN54LS00, SN54S00 SN7400, SN74LS00, SN74S00 QUADRUPLE 2-INPUT POSITIVE-NAND GATES SDLS025 - DECEMBER 1983 - REVISED MARCH 1988

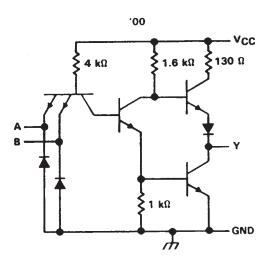

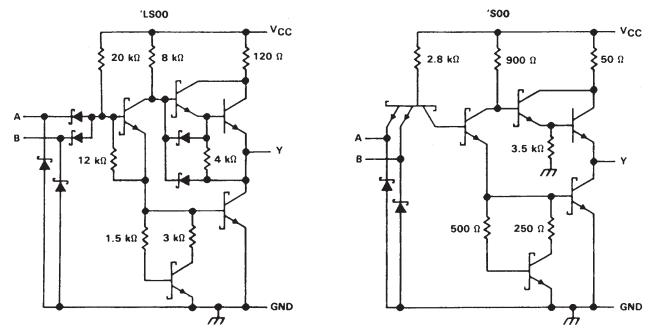

#### schematics (each gate)

Resistor values shown are nominal.

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, Vcc (see Note 1)      |         | 7 V            |

|---------------------------------------|---------|----------------|

| Input voltage: '00, 'S00              |         | 5.5 V          |

| ′LS00                                 |         | 7 V            |

| Operating free-air temperature range: | : SN54' | –55°C to 125°C |

|                                       | SN74'   | 0°C to 70°C    |

| Storage temperature range             |         | -65°C to 150°C |

NOTE 1: Voltage values are with respect to network ground terminal.

# SN5400, SN54LS00, SN54S00 SN7400, SN74LS00, SN74S00 QUADRUPLE 2-INPUT POSITIVE-NAND GATES

SDLS025 - DECEMBER 1983 - REVISED MARCH 1988

#### recommended operating conditions

|                 | · · · · · · · · · · · · · · · · · · · |      | SN5400 |     |      |     |       |      |

|-----------------|---------------------------------------|------|--------|-----|------|-----|-------|------|

|                 |                                       | MIN  | NOM    | MAX | MIN  | NOM | MAX   | UNIT |

| v <sub>cc</sub> | Supply voltage                        | 4.5  | 5      | 5.5 | 4.75 | 5   | 5.25  | v    |

| VIH             | High-level input voltage              | 2    |        |     | 2    |     |       | v    |

| VIL             | Low-level input voltage               |      |        | 0.8 |      |     | 0.8   | v    |

| юн              | High-level output current             |      |        | 0.4 |      |     | - 0.4 | mA   |

| IOL             | Low-level output current              |      |        | 16  |      |     | 16    | mA   |

| т <sub>А</sub>  | Operating free-air temperature        | - 55 |        | 125 | 0    |     | 70    | °c   |

#### electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|                   | ~~~                                    |            |                            |     |      | SN5400 | )     |      |     |       |    |

|-------------------|----------------------------------------|------------|----------------------------|-----|------|--------|-------|------|-----|-------|----|

| PARAMETER         | TEST CONDITIONS T                      |            |                            | MIN | TYP‡ | MAX    | MIN   | түр‡ | MAX | UNIT  |    |

| VIK               | V <sub>CC</sub> = MIN, II =            | = 12 mA    |                            |     |      |        | - 1.5 |      |     | - 1.5 | V  |

| VOH               | V <sub>CC</sub> = MIN, VII             | L = 0.8 V, | 1 <sub>OH</sub> ≈ – 0.4 mA |     | 2.4  | 3.4    |       | 2.4  | 3.4 |       | V  |

| VOL               | V <sub>CC</sub> = MIN, V <sub>II</sub> | H = 2 V,   | I <sub>OL</sub> = 16 mA    |     |      | 0.2    | 0.4   |      | 0.2 | 0.4   | V  |

| - Ij              | V <sub>CC</sub> = MAX, V <sub>1</sub>  | = 5.5 V    |                            |     |      |        | 1     |      |     | 1     | mA |

| Чн                | V <sub>CC</sub> = MAX, V <sub>I</sub>  | = 2.4 V    |                            |     |      |        | 40    |      |     | 40    | μA |

| ΠL                | V <sub>CC</sub> = MAX, V <sub>I</sub>  | = 0.4 V    |                            |     |      |        | - 1.6 |      |     | - 1.6 | mA |

| I <sub>OS</sub> § | V <sub>CC</sub> = MAX                  |            |                            |     | - 20 |        | - 55  | - 18 |     | - 55  | mA |

| 1ссн              | V <sub>CC</sub> = MAX, V <sub>I</sub>  | = 0 V      |                            |     |      | 4      | 8     |      | 4   | 8     | mA |

| ICCL              | V <sub>CC</sub> = MAX, V <sub>1</sub>  | = 4.5 V    |                            |     |      | 12     | 22    |      | 12  | 22    | mA |

† For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

‡ All typical values are at  $V_{CC}$  = 5 V, T<sub>A</sub> = 25<sup>o</sup>C. § Not more than one output should be shorted at a time.

### switching characteristics, $V_{CC} = 5 V$ , $T_A = 25^{\circ}C$ (see note 2)

| PARAMETER        | FROM<br>(INPUT) | TO<br>(OUTPUT) | TEST CONDITIONS                                | MIN | түр | MAX | UNIT |

|------------------|-----------------|----------------|------------------------------------------------|-----|-----|-----|------|

| <sup>t</sup> PLH |                 |                |                                                |     | 11  | 22  | ns   |

| <sup>t</sup> PHL | A or B          | Y              | R <sub>L</sub> = 400 Ω, C <sub>L</sub> = 15 pF |     | 7   | 15  | ns   |

## SN5400, SN54LS00, SN54S00 SN7400, SN74LS00, SN74S00 **QUADRUPLE 2-INPUT POSITIVE-NAND GATES**

SDLS025 - DECEMBER 1983 - REVISED MARCH 1988

#### recommended operating conditions

|                      |                             |      | SN54LS00 |       |      | SN74LS00 |       |      |  |

|----------------------|-----------------------------|------|----------|-------|------|----------|-------|------|--|

|                      |                             | MIN  | NOM      | MAX   | MIN  | NOM      | MAX   | UNIT |  |

| V <sub>CC</sub> Supp | oly voltage                 | 4.5  | 5        | 5.5   | 4.75 | 5        | 5.25  | V    |  |

| VIH High             | n-level input voltage       | 2    |          |       | 2    |          |       | V    |  |

| VIL Low              | -level input voltage        |      |          | 0.7   |      |          | 0.8   | v    |  |

| IOH High             | level output current        |      |          | - 0.4 |      |          | - 0.4 | mA   |  |

| IOL LOW              | level output current        |      |          | 4     |      |          | 8     | mA   |  |

| T <sub>A</sub> Ope   | rating free-air temperature | - 55 |          | 125   | 0    |          | 70    | °C   |  |

#### electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|                 |                        |                          |                                       |      | SN54LS00                               |       |      | SN74LS00 |       |      |

|-----------------|------------------------|--------------------------|---------------------------------------|------|----------------------------------------|-------|------|----------|-------|------|

| PARAMETER       |                        | TEST CONDITIONS T        |                                       |      | TYP‡                                   | MAX   | MIN  | TYP‡     | MAX   | UNIT |

| VIK             | V <sub>CC</sub> = MIN, | 1 <sub>1</sub> = - 18 mA | · · · · · · · · · · · · · · · · · · · |      |                                        | - 1.5 |      |          | - 1.5 | v    |

| V <sub>OH</sub> | V <sub>CC</sub> = MIN, | VIL = MAX,               | I <sub>OH</sub> = - 0.4 mA            | 2.5  | 3.4                                    |       | 2.7  | 3.4      |       | V    |

|                 | V <sub>CC</sub> = MIN, | V <sub>IH</sub> = 2 V,   | IOL = 4 mA                            |      | 0.25                                   | 0.4   |      | 0.25     | 0.4   | v    |

| VOL             | V <sub>CC</sub> = MIN, | V <sub>IH</sub> = 2 V,   | IOL = 8 mA                            |      | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |       |      | 0.35     | 0.5   | ] `  |

| ŧ               | V <sub>CC</sub> = MAX, | V <sub>I</sub> = 7 V     |                                       |      |                                        | 0.1   |      |          | 0.1   | mA   |

| цн              | V <sub>CC</sub> = MAX, | V <sub>1</sub> = 2.7 V   |                                       |      |                                        | 20    |      |          | 20    | μA   |

| ΊL              | V <sub>CC</sub> = MAX, | V1 = 0.4 V               |                                       |      |                                        | - 0.4 |      |          | - 0.4 | mA   |

| IOS§            | V <sub>CC</sub> = MAX  |                          |                                       | - 20 |                                        | - 100 | - 20 |          | - 100 | mA   |

| Іссн            | V <sub>CC</sub> = MAX, | V <sub>1</sub> = 0 V     |                                       |      | 0.8                                    | 1.6   |      | 0.8      | 1.6   | mA   |

| ICCL            | V <sub>CC</sub> = MAX, | V <sub>1</sub> = 4.5 V   |                                       |      | 2.4                                    | 4.4   |      | 2.4      | 4.4   | mA   |

† For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

$\ddagger$  All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25<sup>o</sup>C § Not more than one output should be shorted at a time, and the duration of the short-circuit should not exceed one second.

### switching characteristics, $V_{CC} = 5 V$ , $T_A = 25^{\circ}C$ (see note 2)

| PARAMETER        | FROM<br>(INPUT) | TO<br>(OUTPUT) | TEST COND                | DITIONS    | MIN | түр | МАХ | UNIT |

|------------------|-----------------|----------------|--------------------------|------------|-----|-----|-----|------|

| tPLH             | A B             | ×              | $P_{\rm c} = 2 k \Omega$ | 0 15 of    |     | 9   | 15  | ns   |

| <sup>t</sup> PHL | A or B          | Ŧ              | $R_{L} = 2 k \Omega$ ,   | CL = 15 pF |     | 10  | 15  | ns   |

## SN5400, SN54LS00, SN54S00 SN7400, SN74LS00, SN74S00 **QUADRUPLE 2-INPUT POSITIVE-NAND GATES**

SDLS025 – DECEMBER 1983 – REVISED MARCH 1988

#### recommended operating conditions

|     |                                |      | SN54S00 |     |      | SN74S00 |      |      |  |

|-----|--------------------------------|------|---------|-----|------|---------|------|------|--|

|     |                                | MIN  | NOM     | MAX | MIN  | NOM     | MAX  | UNIT |  |

| Vcc | Supply voltage                 | 4.5  | 5       | 5.5 | 4.75 | 5       | 5.25 | V    |  |

| VIH | High-level input voltage       | 2    |         |     | 2    |         |      | v    |  |

| VIL | Low-level input voltage        |      |         | 0.8 |      |         | 0.8  | v    |  |

| юн  | High-level output current      |      |         | - 1 |      |         | - 1  | mA   |  |

| IOL | Low-level output current       |      |         | 20  |      |         | 20   | mΑ   |  |

| TA  | Operating free-air temperature | - 55 |         | 125 | 0    |         | 70   | °C   |  |

#### electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|                   |                        |                              |                          | SN54S00 |      |      | SN74S00 |      |      |      |

|-------------------|------------------------|------------------------------|--------------------------|---------|------|------|---------|------|------|------|

| PARAMETER         |                        | TEST CONDITIONS <sup>†</sup> |                          | MIN     | TYP‡ | MAX  | MIN     | TYP‡ | MAX  | UNIT |

| VIK               | V <sub>CC</sub> = MIN, | I <sub>I</sub> = -18 mA      |                          |         |      | -1.2 |         |      | -1.2 | v    |

| VOH               | V <sub>CC</sub> = MIN, | V <sub>IL</sub> = 0.8 V,     | <sup>I</sup> OH = - 1 mA | 2.5     | 3.4  |      | 2.7     | 3.4  |      | v    |

| VOL               | V <sub>CC</sub> = MIN, | V <sub>IH</sub> = 2 V,       | I <sub>OL</sub> = 20 mA  |         |      | 0.5  |         |      | 0.5  | v    |

|                   | V <sub>CC</sub> = MAX, | V <sub>I</sub> = 5.5 V       |                          |         |      | 1    |         |      | 1    | mA   |

| Чн                | V <sub>CC</sub> = MAX, | V <sub>1</sub> = 2.7 V       |                          |         |      | 50   |         |      | 50   | μA   |

| 41                | V <sub>CC</sub> = MAX, | V <sub>1</sub> = 0.5 V       |                          |         |      | -2   |         |      | -2   | mA   |

| I <sub>OS</sub> § | V <sub>CC</sub> = MAX  |                              |                          | -40     |      | -100 | -40     |      | -100 | mA   |

| Іссн              | V <sub>CC</sub> = MAX, | V1 = 0 V                     |                          |         | 10   | 16   |         | 10   | 16   | mA   |

| ICCL              | V <sub>CC</sub> = MAX, | V <sub>1</sub> = 4.5 V       |                          |         | 20   | 36   |         | 20   | 36   | mA   |

† For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

‡ All typical values are at  $V_{CC} = 5 V$ ,  $T_A = 25^{\circ}C$ .

§ Not more than one output should be shorted at a time, and the duration of the short-circuit should not exceed one second.

### switching characteristics, $V_{CC} = 5 V$ , $T_A = 25^{\circ}C$ (see note 2)

| PARAMETER        | FROM<br>(INPUT) | TO<br>(OUTPUT) | TEST CONDITIONS                                | MIN TYP | MAX | UNIT |

|------------------|-----------------|----------------|------------------------------------------------|---------|-----|------|

| <sup>t</sup> PLH |                 | or B Y         | R <sub>1</sub> = 280 Ω, C <sub>L</sub> = 15 pF | 3       | 4.5 | ns   |

| <sup>t</sup> PHL |                 |                |                                                | 3       | 5   | ns   |

| tPLH             | A or B          |                |                                                | 4.5     |     | ns   |

| <sup>t</sup> PHL |                 |                | R <sub>L</sub> = 280 Ω, C <sub>L</sub> = 50 pF | 5       |     | ns   |

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1999, Texas Instruments Incorporated

DM74LS04 Hex Inverting Gates

## SEMICONDUCTOR

FAIRCHILD

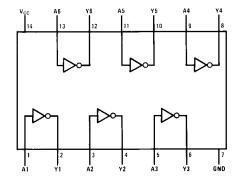

## DM74LS04 Hex Inverting Gates

#### **General Description**

This device contains six independent gates each of which performs the logic INVERT function.

#### **Ordering Code:**

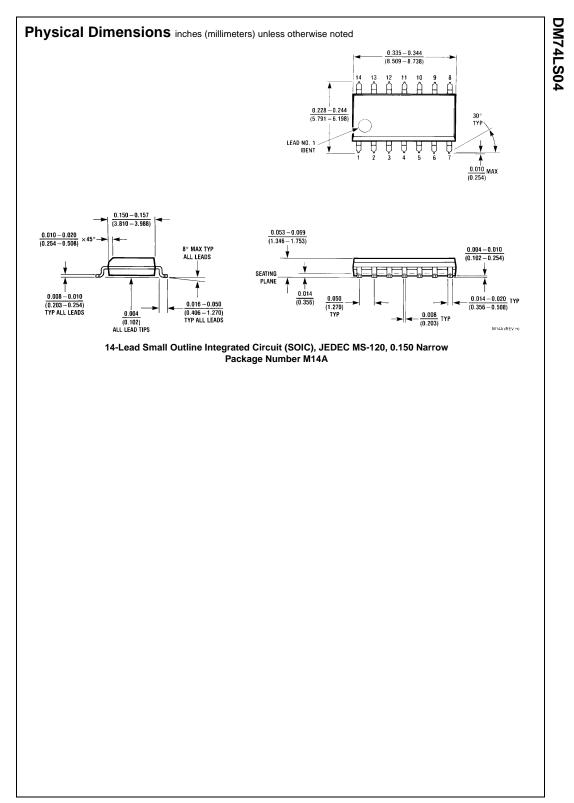

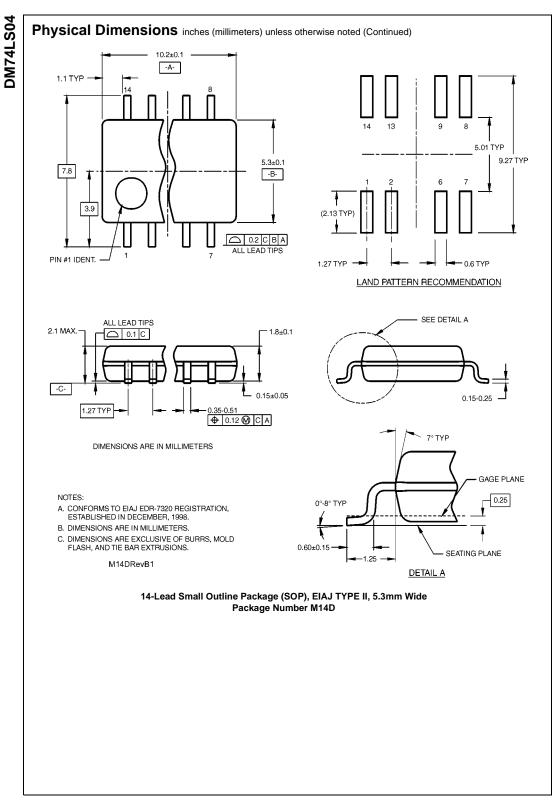

| Order Number | Package Number | Package Description                                                         |

|--------------|----------------|-----------------------------------------------------------------------------|

| DM74LS04M    | M14A           | 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150 Narrow |

| DM74LS04SJ   | M14D           | 14-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide               |

| DM74LS04N    | N14A           | 14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide       |

Devices also available in Tape and Reel. Specify by appending the suffix letter "X" to the ordering code.

#### **Connection Diagram**

### Function Table

$\mathbf{Y} = \overline{\mathbf{A}}$

| Input | Output |

|-------|--------|

| A     | Y      |

| L     | Н      |

| н     | L      |

H = HIGH Logic Level L = LOW Logic Level

### Absolute Maximum Ratings(Note 1)

| Supply Voltage                       | 7V                             |

|--------------------------------------|--------------------------------|

| Input Voltage                        | 7V                             |

| Operating Free Air Temperature Range | $0^{\circ}C$ to $+70^{\circ}C$ |

| Storage Temperature Range            | -65°C to +150°C                |

Note 1: The "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the absolute maximum ratings. The "Recommended Operating Conditions" table will define the conditions for actual device operation.

#### **Recommended Operating Conditions**

| Symbol          | Parameter                      | Min  | Nom | Max  | Units |

|-----------------|--------------------------------|------|-----|------|-------|

| V <sub>CC</sub> | Supply Voltage                 | 4.75 | 5   | 5.25 | V     |

| √ <sub>IH</sub> | HIGH Level Input Voltage       | 2    |     |      | V     |

| V <sub>IL</sub> | LOW Level Input Voltage        |      |     | 0.8  | V     |

| ОН              | HIGH Level Output Current      |      |     | -0.4 | mA    |

| OL              | LOW Level Output Current       |      |     | 8    | mA    |

| T <sub>A</sub>  | Free Air Operating Temperature | 0    |     | 70   | °C    |

#### **Electrical Characteristics**

over recommended operating free air temperature range (unless otherwise noted)

| Symbol           | Parameter                        | Conditions                                      | Min | Typ<br>(Note 2) | Max   | Units |

|------------------|----------------------------------|-------------------------------------------------|-----|-----------------|-------|-------|

| VI               | Input Clamp Voltage              | $V_{CC} = Min, I_I = -18 \text{ mA}$            |     |                 | -1.5  | V     |

| V <sub>OH</sub>  | HIGH Level<br>Output Voltage     | $V_{CC} = Min, I_{OH} = Max,$<br>$V_{IL} = Max$ | 2.7 | 3.4             |       | V     |

| V <sub>OL</sub>  | LOW Level<br>Output Voltage      | $V_{CC} = Min, I_{OL} = Max,$<br>$V_{IH} = Min$ |     | 0.35            | 0.5   | V     |

|                  |                                  | $I_{OL} = 4 \text{ mA}, V_{CC} = Min$           |     | 0.25            | 0.4   |       |

| I <sub>I</sub>   | Input Current @ Max              | $V_{CC} = Max, V_I = 7V$                        |     |                 | 0.1   | mA    |

|                  | Input Voltage                    |                                                 |     |                 |       |       |

| I <sub>IH</sub>  | HIGH Level Input Current         | $V_{CC} = Max, V_I = 2.7V$                      |     |                 | 20    | μΑ    |

| Ι <sub>ΙL</sub>  | LOW Level Input Current          | $V_{CC} = Max, V_I = 0.4V$                      |     |                 | -0.36 | mA    |

| los              | Short Circuit Output Current     | V <sub>CC</sub> = Max (Note 3)                  | -20 |                 | -100  | mA    |

| ICCH             | Supply Current with Outputs HIGH | V <sub>CC</sub> = Max                           |     | 1.2             | 2.4   | mA    |

| I <sub>CCL</sub> | Supply Current with Outputs LOW  | V <sub>CC</sub> = Max                           |     | 3.6             | 6.6   | mA    |

Note 2: All typicals are at  $V_{CC} = 5V$ ,  $T_A = 25^{\circ}C$ .

Note 3: Not more than one output should be shorted at a time, and the duration should not exceed one second.

#### **Switching Characteristics**

at  $V_{CC}=5V$  and  $T_A=25^\circ C$

| Symbol Parameter |                                                    | C <sub>L</sub> = 1 | 15 pF | C <sub>L</sub> = 5 | Units |    |

|------------------|----------------------------------------------------|--------------------|-------|--------------------|-------|----|

|                  |                                                    | Min                | Max   | Min                | Max   |    |

| t <sub>PLH</sub> | Propagation Delay Time<br>LOW-to-HIGH Level Output | 3                  | 10    | 4                  | 15    | ns |

| t <sub>PHL</sub> | Propagation Delay Time<br>HIGH-to-LOW Level Output | 3                  | 10    | 4                  | 15    | ns |

DM74LS04 Hex Inverting Gates

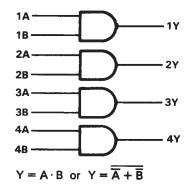

#### SN5408, SN54LS08, SN54S08 SN7408, SN74LS08, SN74S08 QUADRUPLE 2-INPUT POSITIVE-AND GATES SDLS033 – DECEMBER 1983 – REVISED MARCH 1988

- Package Options Include Plastic "Small Outline" Packages, Ceramic Chip Carriers and Flat Packages, and Plastic and Ceramic DIPs

- Dependable Texas Instruments Quality and Reliability

#### description

These devices contain four independent 2-input AND gates.

The SN5408, SN54LS08, and SN54S08 are characterized for operation over the full military temperature range of -55 °C to 125 °C. The SN7408, SN74LS08 and SN74S08 are characterized for operation from 0° to 70 °C.

| INP | UTS | OUTPUT |

|-----|-----|--------|

| A   | в   | Y      |

| н   | н   | н      |

| L   | х   | L      |

| X   | L   | L.     |

logic symbol<sup>†</sup>

<sup>†</sup> This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

Pin numbers shown are for D, J, N, and W packages.

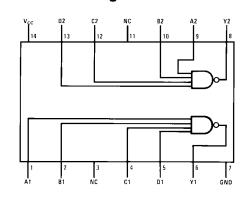

SN5408, SN54LS08, SN54S08 . . . J OR W PACKAGE SN7408 . . . J OR N PACKAGE SN74LS08, SN74S08 . . . D, J OR N PACKAGE

#### (TOP VIEW)

| 1A<br>1B<br>1Y<br>2A<br>2B | 1<br>2<br>3<br>4<br>5 | 14 VCC<br>13 4B<br>12 4A<br>11 4Y<br>10 3B |

|----------------------------|-----------------------|--------------------------------------------|

|                            | 4                     | Г                                          |

| 2B 🗌                       |                       | 10 3B                                      |

| 2Y 🗋                       | 6                     | 9 🗍 <b>3A</b>                              |

|                            | 7                     | 8 <b>]] 3Y</b>                             |

SN54LS08, SN54S08 . . . FK PACKAGE (TOP VIEW)

NC-No internal connection

logic diagram (positive logic)

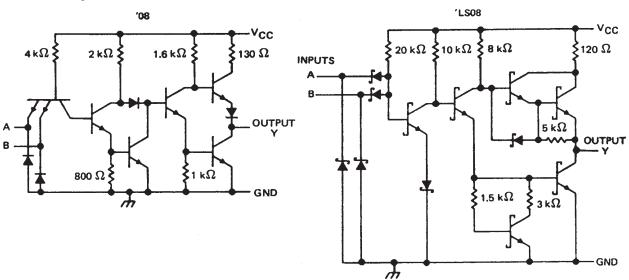

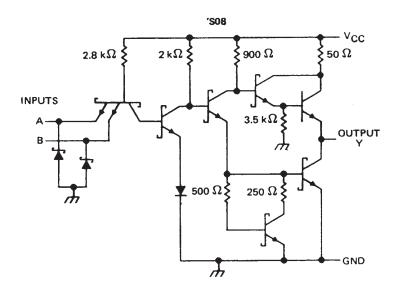

### SN5408, SN54LS08, SN54S08 SN7408, SN74LS08, SN74S08 **QUADRUPLE 2-INPUT POSITIVE-AND GATES**

SDLS033 – DECEMBER 1983 – REVISED MARCH 1988

#### schematics (each gate)

Resistor values are nominal.

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, V <sub>CC</sub> (see Note 1) |                                                |

|----------------------------------------------|------------------------------------------------|

| Input voltage: '08, 'S08                     | 5.5 V                                          |

| 'LS08                                        |                                                |

| Operating free-air temperature range: SN54'  |                                                |

| SN74′                                        | 0°C to 70°C                                    |

| Storage temperature range                    | $\dots \dots -65^{\circ}$ C to $150^{\circ}$ C |

NOTE 1: Voltage values are with respect to network ground terminal.

## SN5408, SN54LS08, SN54S08 SN7408, SN74LS08, SN74S08 QUADRUPLE 2-INPUT POSITIVE-AND GATES SDLS033 - DECEMBER 1983 - REVISED MARCH 1988

#### recommended operating conditions

|                                               |      | SN5408 |       |      | SN7408 |       |      |

|-----------------------------------------------|------|--------|-------|------|--------|-------|------|

|                                               | MIN  | NOM    | MAX   | MIN  | NOM    | мах   | UNIT |

| V <sub>CC</sub> Supply voltage                | 4.5  | 5      | 5.5   | 4.75 | 5      | 5.25  | v    |

| VIH High-level input voltage                  | 2    |        |       | 2    |        |       | v    |

| VIL Low-level input voltage                   |      |        | 0.8   |      |        | 0.8   | v    |

| IOH High-level output current                 |      |        | - 0.8 |      |        | - 0.8 | mA   |

| IOL Low-level output current                  |      |        | 16    |      |        | 16    | mA   |

| T <sub>A</sub> Operating free-air temperature | - 55 |        | 125   | 0    |        | 70    | °c   |

## electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|           |                                                                         |      | SN540 | 3     |      | SN740 | 8     |      |

|-----------|-------------------------------------------------------------------------|------|-------|-------|------|-------|-------|------|

| PARAMETER | TEST CONDITIONS T                                                       | MIN  | TYP‡  | MAX   | MIN  | түр‡  | МАХ   | UNIT |

| VIK       | V <sub>CC</sub> = MIN, I <sub>t</sub> = - 12 mA                         |      |       | - 1.5 |      |       | - 1.5 | V    |

| ∨он       | $V_{CC} = MIN, V_{1H} = 2V, I_{OH} = -0.8 \text{ mA}$                   | 2.4  | 3.4   |       | 2.4  | 3.4   |       | .V.  |

| VOL       | V <sub>CC</sub> = MIN, V <sub>IL</sub> = 0.8 V, I <sub>OL</sub> = 16 mA |      | 0.2   | 0.4   |      | 0.2   | 0.4   | v    |

| lį        | V <sub>CC</sub> = MAX, V <sub>I</sub> = 5.5 V                           |      |       | 1     |      |       | 1     | mA   |

| Чн        | V <sub>CC</sub> = MAX, V <sub>1</sub> = 2.4 V                           |      |       | 40    |      |       | 40    | μA   |

| μL        | V <sub>CC</sub> = MAX, V <sub>1</sub> = 0.4 V                           |      |       | - 1.6 |      |       | - 1.6 | mA   |

| IOS §     | V <sub>CC</sub> = MAX                                                   | - 20 |       | - 55  | - 18 |       | - 55  | mA   |

| ICCH      | V <sub>CC</sub> = MAX, V <sub>I</sub> = 4.5 V                           |      | 11    | 21    |      | 11    | 21    | mA   |

| ICCL      | V <sub>CC</sub> = MAX, V <sub>l</sub> = 0 V                             |      | 20    | 33    |      | 20    | 33    | mA   |

† For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

‡ All typical values are at  $V_{CC} = 5 V$ ,  $T_A = 25^{\circ}C$ . § Not more than one output should be shorted at a time.

## switching characteristics, $V_{CC} = 5 V$ , $T_A = 25^{\circ}C$ (see note 2)

| PARAMETER        | FROM<br>(INPUT) | TO<br>(OUTPUT) | TEST CONDITIONS                                | MIN | ТҮР  | MAX | UNIT |

|------------------|-----------------|----------------|------------------------------------------------|-----|------|-----|------|

| <sup>t</sup> PLH |                 |                |                                                |     | 17.5 | 27  | ns   |

| tPHL             | A or B          | Y              | R <sub>L</sub> = 400 Ω, C <sub>L</sub> = 15 pF |     | 12   | 19  | ns   |

NOTE 2: Load circuits and voltage waveforms are shown in Section 1.

i

## SN5408, SN54LS08, SN54S08 SN7408, SN74LS08, SN74S08 **QUADRUPLE 2-INPUT POSITIVE-AND GATES**

SDLS033 – DECEMBER 1983 – REVISED MARCH 1988

#### recommended operating conditions

|                                               |      | SN54LS08 |       | SN74LS08 |     |       | UNIT |

|-----------------------------------------------|------|----------|-------|----------|-----|-------|------|

|                                               | MIN  | NOM      | MAX   | MIN      | NOM | MAX   | UNIT |

| V <sub>CC</sub> Supply voltage                | 4.5  | 5        | 5.5   | 4.75     | 5   | 5.25  | v    |

| VIH High-level input voltage                  | 2    |          |       | 2        |     |       | v    |

| VIL Low-level input voltage                   |      |          | 0.7   |          |     | 0.8   | v    |

| IOH High-level output current                 |      |          | - 0.4 |          |     | - 0.4 | mA   |

| IOL Low-level output current                  |      |          | 4     |          |     | 8     | mA   |

| T <sub>A</sub> Operating free-air temperature | - 55 |          | 125   | 0        |     | 70    | °C   |

#### electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|           |                        | TEST CONDITIONS T      |                            |      | SN64LS | 08    |      | SN74LS | 08    |      |

|-----------|------------------------|------------------------|----------------------------|------|--------|-------|------|--------|-------|------|

| PARAMETER |                        | TEST CONDIT            | TIONS T                    | MIN  | TYP‡   | MAX   | MIN  | TYP‡   | MAX   | UNIT |

| VIK       | V <sub>CC</sub> = MIN, | lı = — 18 mA           |                            |      |        | - 1.5 |      |        | - 1.5 | V    |

| VOH       | V <sub>CC</sub> = MIN, | V <sub>IH</sub> = 2 V, | <sup>I</sup> OH = - 0.4 mA | 2.5  | 3.4    |       | 2.7  | 3.4    |       | v    |

|           | V <sub>CC</sub> = MIN, | V <sub>1L</sub> ≈ MAX, | I <sub>OL</sub> = 4 mA     |      | 0.25   | 0.4   |      | 0.25   | 0.4   | v    |

| VOL       | V <sub>CC</sub> = MIN, | VIL = MAX,             | IOL = 8 mA                 |      |        |       |      | 0.35   | 0.5   |      |

| 1         | V <sub>CC</sub> = MAX, | V1 = 7 V               |                            |      |        | 0.1   |      |        | 0.1   | mA   |

| ін        | V <sub>CC</sub> = MAX, | V <sub>I</sub> = 2.7 V |                            |      |        | 20    |      |        | 20    | μA   |

| ΊL        | V <sub>CC</sub> = MAX, | V1 = 0.4 V             |                            |      |        | - 0.4 |      |        | - 0.4 | mA   |

| los§      | V <sub>CC</sub> = MAX  |                        |                            | - 20 |        | - 100 | - 20 |        | - 100 | mA   |

| Іссн      | V <sub>CC</sub> = MAX, | V <sub>1</sub> = 4.5 V |                            |      | 2.4    | 4.8   |      | 2.4    | 4,8   | mA   |

| ICCL      | V <sub>CC</sub> = MAX, | V1 = 0 V               |                            |      | 4.4    | 8.8   |      | 4.4    | 8.8   | mA   |

† For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

‡ All typical values are at  $V_{CC} = 5 V$ ,  $T_A = 25^{\circ}C$ § Not more than one output should be shorted at a time, and the duration of the short-circuit should not exceed one second.

#### switching characteristics, $V_{CC} = 5 V$ , $T_A = 25^{\circ}C$ (see note 2)

| PARAMETER        | FROM<br>(INPUT) | TO<br>(OUTPUT) | TEST CON            | DITIONS                | MIN | түр | мах | UNIT |

|------------------|-----------------|----------------|---------------------|------------------------|-----|-----|-----|------|

| <sup>t</sup> PLH | A or B          | ×              | $R_1 = 2 k\Omega$ , | C <sub>1</sub> = 15 pF |     | 8   | 15  | ns   |

| <sup>t</sup> PHL | AOIB            | Ŧ              | n 2 ksz,            | CL - 13 pr             |     | 10  | 20  | ns   |

## SN5408, SN54LS08, SN54S08 SN7408, SN74LS08, SN74S08 **QUADRUPLE 2-INPUT POSITIVE-AND GATES** SDLS033 – DECEMBER 1983 – REVISED MARCH 1988

#### recommended operating conditions

|                    |                               |      | SN54S0 | 8   |      | SN74S0 | 8    | UNIT |

|--------------------|-------------------------------|------|--------|-----|------|--------|------|------|

|                    |                               | MIN  | NOM    | MAX | MIN  | NOM    | MAX  | UNIT |

| V <sub>CC</sub> Su | ipply voltage                 | 4.5  | 5      | 5.5 | 4.75 | 5      | 5.25 | v    |

| VIH Hi             | gh-level input voltage        | 2    |        |     | 2    |        |      | v    |

| VIL LO             | ow-level input voltage        |      |        | 0.8 |      | _      | 0.8  | v    |

| IOH Hi             | gh-level output current       |      |        | - 1 |      | _      | - 1  | mA   |

| IOL LO             | ow-level output current       |      |        | 20  |      |        | 20   | mA   |

| TA O               | perating free-air temperature | - 55 |        | 125 | 0    |        | 70   | °c   |

#### electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|                | TEST CONDITIONS †      |                         |                         | SN54S0 | 8   |      | 8    | UNIT |      |    |

|----------------|------------------------|-------------------------|-------------------------|--------|-----|------|------|------|------|----|

| PARAMETER      |                        |                         | MIN                     | TYP‡   | MAX | MIN  | TYP‡ | MAX  | UNIT |    |

| VIK            | V <sub>CC</sub> = MIN, | l <sub>1</sub> = -18 mA |                         |        |     | -1.2 |      |      | -1.2 | v  |

| VOH            | V <sub>CC</sub> = MIN, | V <sub>IH</sub> = 2 V,  | IOH = - 1 mA            | 2.5    | 3.4 |      | 2.7  | 3.4  |      | v  |

| VOL            | V <sub>CC</sub> = MIN, | V <sub>IL</sub> = 0.8 V | 1 <sub>OL</sub> = 20 mA |        |     | 0.5  |      |      | 0.5  | v  |

| l <sub>l</sub> | V <sub>CC</sub> = MAX, | VI ≈ 5.5 V              |                         |        |     | 1    |      |      | 1    | mA |

| ін             | V <sub>CC</sub> = MAX, | V <sub>1</sub> = 2.7 V  |                         |        |     | 50   |      |      | 50   | μA |

| μL             | V <sub>CC</sub> = MAX, | V <sub>1</sub> = 0.5 V  |                         |        |     | -2   |      |      | 2    | mA |

| los§           | V <sub>CC</sub> = MAX  |                         |                         | -40    |     | -100 | -40  |      | 100  | mA |

| ICCH           | V <sub>CC</sub> = MAX, | V <sub>I</sub> = 4.5 V  | <u> </u>                |        | 18  | 32   |      | 18   | 32   | mA |

| ICCL           | V <sub>CC</sub> = MAX, | VI = 0 V                |                         |        | 32  | 57   |      | 32   | 57   | mA |

† For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

‡ All typical values are at  $V_{CC} = 5 V$ ,  $T_A = 25^{\circ}C$ . § Not more than one output should be shorted at a time, and the duration of the short-circuit should not exceed one second.

| PARAMETER        | FROM<br>(INPUT) | то<br>(оитрит) | TEST CONDITIONS                                |  | түр | MAX | UNIT |

|------------------|-----------------|----------------|------------------------------------------------|--|-----|-----|------|

| <sup>t</sup> PLH |                 |                | R <sub>I</sub> = 280 Ω, C <sub>L</sub> = 15 pF |  | 4.5 | 7   | ns   |

| <sup>t</sup> PHL |                 | v              | HL-20032, CE-130                               |  | 5   | 7,5 | ns   |

| <sup>t</sup> PLH | A or B          | Ŷ              | $R_1 = 280 \Omega$ , $C_1 = 50 \rho F$         |  | 6   |     | ns   |

| <sup>t</sup> PHL |                 |                | R <sub>L</sub> = 280 Ω, C <sub>L</sub> = 50 ρF |  | 7,5 |     | ns   |

#### switching characteristics, $V_{CC} = 5 V$ , $T_A = 25^{\circ}C$ (see note 2)

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1999, Texas Instruments Incorporated

DM74LS20 Dual 4-Input NAND Gate

## FAIRCHILD

SEMICONDUCTOR

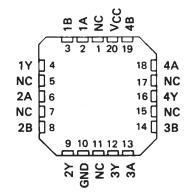

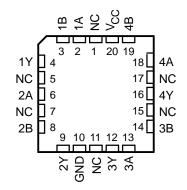

## DM74LS20 Dual 4-Input NAND Gate

#### **General Description**

This device contains two independent gates each of which performs the logic NAND function.

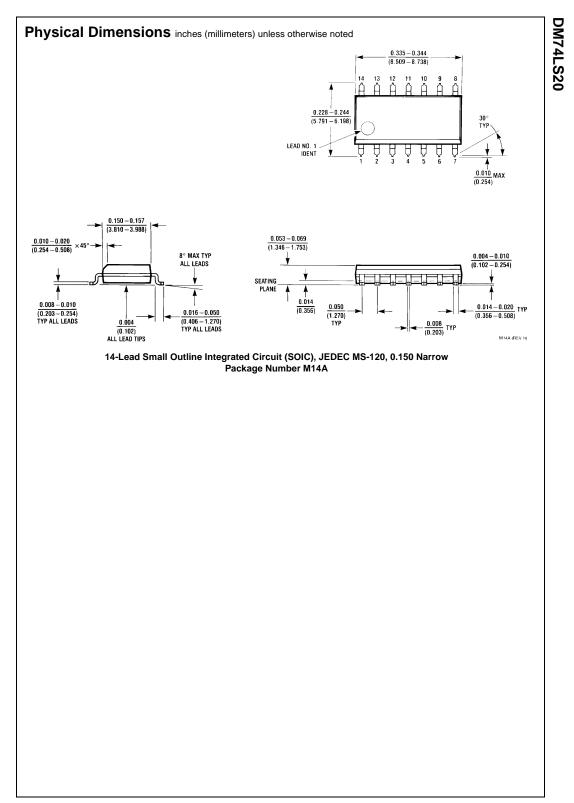

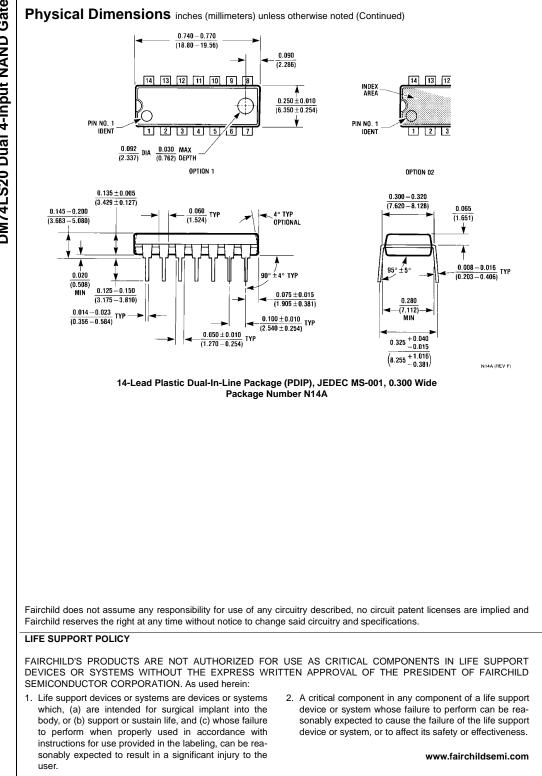

#### **Ordering Code:**

| Order Number           | Package Number                                                                                            | Package Description                                                         |  |  |  |  |  |  |

|------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--|--|--|--|--|--|

| DM74LS20M              | M14A                                                                                                      | 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150 Narrow |  |  |  |  |  |  |

| DM74LS20N              | N14A                                                                                                      | 14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide       |  |  |  |  |  |  |

| Devices also available | Devices also available in Tape and Reel. Specify by appending the suffix letter "X" to the ordering code. |                                                                             |  |  |  |  |  |  |

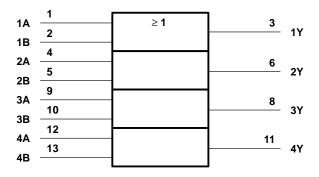

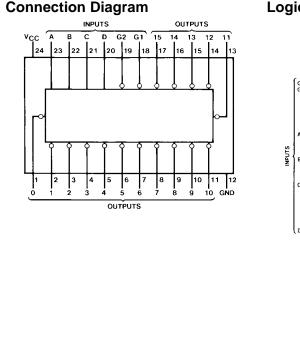

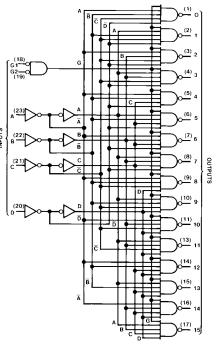

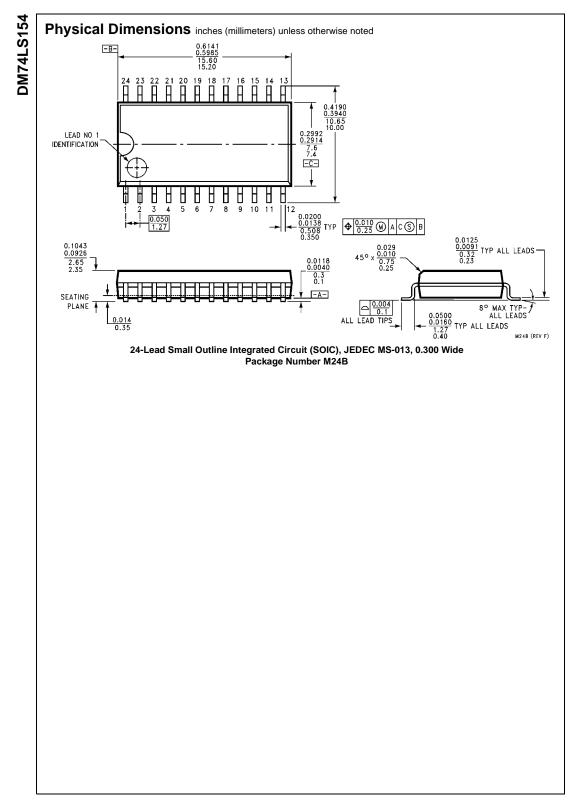

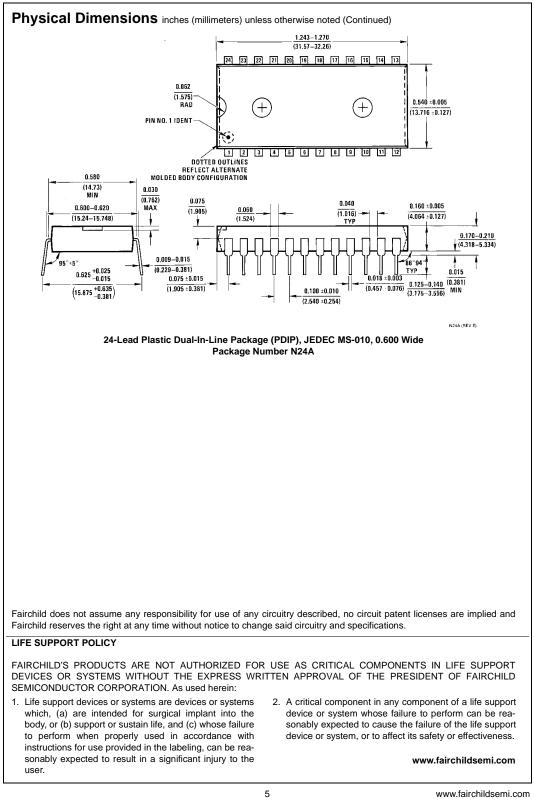

## Connection Diagram

#### Function Table

Y = ABCD

|   | Inp | outs |   | Output |

|---|-----|------|---|--------|

| Α | В   | С    | D | Y      |

| Х | Х   | Х    | L | Н      |

| Х | Х   | L    | Х | Н      |

| Х | L   | Х    | Х | Н      |

| L | Х   | х    | Х | н      |

| н | н   | н    | н | L      |

H = HIGH Logic Level

L = LOW Logic Level X = Either LOW or HIGH Logic Level

#### Absolute Maximum Ratings(Note 1)

| Supply Voltage                       | 7V                                |

|--------------------------------------|-----------------------------------|

| Input Voltage                        | 7V                                |

| Operating Free Air Temperature Range | $0^{\circ}C$ to $+70^{\circ}C$    |

| Storage Temperature Range            | $-65^{\circ}C$ to $+150^{\circ}C$ |

Note 1: The "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the absolute maximum ratings. The "Recommended Operating Conditions" table will define the conditions for actual device operation.

#### **Recommended Operating Conditions**

| Symbol          | Parameter                      | Min  | Nom | Max  | Units |

|-----------------|--------------------------------|------|-----|------|-------|

| V <sub>CC</sub> | Supply Voltage                 | 4.75 | 5   | 5.25 | V     |

| V <sub>IH</sub> | HIGH Level Input Voltage       | 2    |     |      | V     |

| V <sub>IL</sub> | LOW Level Input Voltage        |      |     | 0.8  | V     |

| он              | HIGH Level Output Current      |      |     | -0.4 | mA    |

| OL              | LOW Level Output Current       |      |     | 8    | mA    |

| T <sub>A</sub>  | Free Air Operating Temperature | 0    |     | 70   | °C    |

#### **Electrical Characteristics**

over recommended operating free air temperature range (unless otherwise noted)

| Symbol           | Parameter                                             | Conditions                                      | Min | Typ<br>(Note 2) | Max   | Units |  |

|------------------|-------------------------------------------------------|-------------------------------------------------|-----|-----------------|-------|-------|--|

| VI               | Input Clamp Voltage                                   | $V_{CC} = Min, I_I = -18 \text{ mA}$            |     |                 | -1.5  | V     |  |

| V <sub>OH</sub>  | HIGH Level<br>Output Voltage                          | $V_{CC} = Min, I_{OH} = Max,$<br>$V_{IL} = Max$ | 2.7 | 3.4             |       | V     |  |

| V <sub>OL</sub>  | LOW Level<br>Output Voltage                           | $V_{CC} = Min, I_{OL} = Max,$<br>$V_{IH} = Min$ |     | 0.35            | 0.5   | v     |  |

|                  |                                                       | $I_{OL} = 4 \text{ mA}, V_{CC} = Min$           |     | 0.25            | 0.4   | ]     |  |

| l <sub>l</sub>   | Input Current @ Max Input Voltage                     | $V_{CC} = Max, V_I = 7V$                        |     |                 | 0.1   | mA    |  |

| I <sub>IH</sub>  | HIGH Level Input Current                              | $V_{CC} = Max, V_I = 2.7V$                      |     |                 | 20    | μΑ    |  |

| IIL              | LOW Level Input Current                               | $V_{CC} = Max, V_I = 0.4V$                      |     |                 | -0.36 | mA    |  |

| los              | Short Circuit Output Current                          | V <sub>CC</sub> = Max (Note 3)                  | -20 |                 | -100  | mA    |  |

| ICCH             | Supply Current with Outputs HIGH                      | V <sub>CC</sub> = Max                           |     | 0.4             | 0.8   | mA    |  |

| I <sub>CCL</sub> | Supply Current with Outputs LOW                       | V <sub>CC</sub> = Max                           |     | 1.2             | 2.2   | mA    |  |

| Note 2: All      | typicals are at $V_{CC} = 5V$ , $T_A = 25^{\circ}C$ . |                                                 |     |                 |       |       |  |

Note 3: Not more than one output should be shorted at a time, and the duration should not exceed one second.

#### **Switching Characteristics**

at  $V_{CC} = 5V$  and  $T_A = 25^{\circ}C$

| Symbol           | Parameter                                          | C <sub>L</sub> = 1 | 15 pF | C <sub>L</sub> = | Units |    |

|------------------|----------------------------------------------------|--------------------|-------|------------------|-------|----|

|                  |                                                    | Min                | Max   | Min              | Max   |    |

| t <sub>PLH</sub> | Propagation Delay Time<br>LOW-to-HIGH Level Output | 3                  | 10    | 4                | 15    | ns |

| t <sub>PHL</sub> | Propagation Delay Time<br>HIGH-to-LOW Level Output | 3                  | 10    | 4                | 15    | ns |

DM74LS20 Dual 4-Input NAND Gate

SDAS113B – APRIL 1982 – REVISED DECEMBER 1994

Package Options Include Plastic Small-Outline (D) Packages, Ceramic Chip Carriers (FK), and Standard Plastic (N) and Ceramic (J) 300-mil DIPs

#### description

These devices contain four independent 2-input positive-OR <u>gates</u>. They perform the Boolean functions  $Y = \overline{A} \cdot \overline{B}$  or Y = A + B in positive logic.

The SN54ALS32 and SN54AS32 are characterized for operation over the full military temperature range of  $-55^{\circ}$ C to  $125^{\circ}$ C. The SN74ALS32 and SN74AS32 are characterized for operation from 0°C to 70°C.

| FUNCTION TABLE<br>(each gate) |     |        |  |  |  |  |  |  |

|-------------------------------|-----|--------|--|--|--|--|--|--|

| INP                           | UTS | OUTPUT |  |  |  |  |  |  |

| Α                             | В   | Y      |  |  |  |  |  |  |

| Н                             | Х   | Н      |  |  |  |  |  |  |

| Х                             | Н   | н      |  |  |  |  |  |  |

| L                             | L   | L      |  |  |  |  |  |  |

#### logic symbol<sup>†</sup>

<sup>†</sup> This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

Pin numbers shown are for the D, J, and N packages.

| SN54ALS32, SN54AS32 J PACKAGE     |

|-----------------------------------|

| SN74ALS32, SN74AS32D OR N PACKAGE |

| (TOP VIEW)                        |

## SN54ALS32, SN54AS32 . . . FK PACKAGE (TOP VIEW)

NC - No internal connection

#### logic diagram (positive logic)

SDAS113B - APRIL 1982 - REVISED DECEMBER 1994

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| Supply voltage, V <sub>CC</sub>                         |                |

|---------------------------------------------------------|----------------|

| Operating free-air temperature range, $T_A$ : SN54ALS32 |                |

| SN74ALS32                                               |                |

| Storage temperature range                               | −65°C to 150°C |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### recommended operating conditions

|                 |                                | SN54ALS32 |     | SN   | UNIT |     |      |    |

|-----------------|--------------------------------|-----------|-----|------|------|-----|------|----|

|                 |                                | MIN       | NOM | MAX  | MIN  | NOM | MAX  |    |

| V <sub>CC</sub> | Supply voltage                 | 4.5       | 5   | 5.5  | 4.5  | 5   | 5.5  | V  |

| VIH             | High-level input voltage       | 2         |     |      | 2    |     |      | V  |

| VIL             | Low-level input voltage        |           |     | 0.8  |      |     | 0.8  | V  |

| ЮН              | High-level output current      |           |     | -0.4 |      |     | -0.4 | mA |

| IOL             | Low-level output current       |           |     | 4    |      |     | 8    | mA |

| TA              | Operating free-air temperature | -55       |     | 125  | 0    |     | 70   | °C |

## electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER        | TEST                       | SN54ALS32 SN74ALS32       |                    |      | SN54ALS32 |                    | 4ALS32 |      |      |

|------------------|----------------------------|---------------------------|--------------------|------|-----------|--------------------|--------|------|------|

| PARAMETER        | IESI C                     | T CONDITIONS              |                    | TYP‡ | MAX       | MIN                | TYP‡   | MAX  | UNIT |

| VIK              | V <sub>CC</sub> = 4.5 V,   | lj = –18 mA               |                    |      | -1.5      |                    |        | -1.5 | V    |

| VOH              | $V_{CC}$ = 4.5 V to 5.5 V, | I <sub>OH</sub> = -0.4 mA | V <sub>CC</sub> -2 | 2    |           | V <sub>CC</sub> -2 | 2      |      | V    |

| VOL              | V <sub>CC</sub> = 4.5 V    | $I_{OL} = 4 \text{ mA}$   |                    | 0.25 | 0.4       |                    | 0.25   | 0.4  | V    |

| VOL              |                            | I <sub>OL</sub> = 8 mA    |                    |      |           |                    | 0.35   | 0.5  | v    |

| lı               | V <sub>CC</sub> = 5.5 V,   | V <sub>I</sub> = 7 V      |                    |      | 0.1       |                    |        | 0.1  | mA   |

| IIH              | V <sub>CC</sub> = 5.5 V,   | V <sub>I</sub> = 2.7 V    |                    |      | 20        |                    |        | 20   | μA   |

| ۱ <sub>IL</sub>  | V <sub>CC</sub> = 5.5 V,   | V <sub>I</sub> = 0.4 V    |                    |      | -0.1      |                    |        | -0.1 | mA   |

| ١ <sub>O</sub> § | V <sub>CC</sub> = 5.5 V,   | V <sub>O</sub> = 2.25 V   | -20                |      | -112      | -30                |        | -112 | mA   |

| Іссн             | V <sub>CC</sub> = 5.5 V,   | V <sub>I</sub> = 4.5 V    |                    | 1.9  | 4         |                    | 1.9    | 4    | mA   |

| ICCL             | V <sub>CC</sub> = 5.5 V,   | V <sub>I</sub> = 0        |                    | 2.6  | 4.9       |                    | 2.6    | 4.9  | mA   |

<sup>‡</sup> All typical values are at  $V_{CC} = 5 V$ ,  $T_A = 25^{\circ}C$ .

\$ The output conditions have been chosen to produce a current that closely approximates one half of the true short-circuit output current, IOS.

#### switching characteristics (see Figure 1)

| PARAMETER        | FROM<br>(INPUT) | то<br>(OUTPUT) | VC<br>CL<br>RL<br>TA | UNIT |       |      |    |

|------------------|-----------------|----------------|----------------------|------|-------|------|----|

|                  |                 |                | SN54A                | LS32 | SN74A | LS32 |    |

|                  |                 |                | MIN                  | MAX  | MIN   | MAX  |    |

| <sup>t</sup> PLH | A or B          | Y              | 3                    | 18   | 3     | 14   |    |

| <sup>t</sup> PHL |                 |                | 3                    | 16   | 3     | 12   | ns |

$\P$  For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

SDAS113B - APRIL 1982 - REVISED DECEMBER 1994

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| Supply voltage, V <sub>CC</sub><br>Input voltage, V <sub>I</sub> |                |

|------------------------------------------------------------------|----------------|

| Operating free-air temperature range, TA: SN54AS32               | –55°C to 125°C |

| SN74AS32                                                         | 0°C to 70°C    |

| Storage temperature range                                        | –65°C to 150°C |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### recommended operating conditions

|     |                                | SN54AS32 |     | S   | UNIT |     |     |      |

|-----|--------------------------------|----------|-----|-----|------|-----|-----|------|

|     |                                | MIN      | NOM | MAX | MIN  | NOM | MAX | UNIT |

| VCC | Supply voltage                 | 4.5      | 5   | 5.5 | 4.5  | 5   | 5.5 | V    |

| VIH | High-level input voltage       | 2        |     |     | 2    |     |     | V    |

| VIL | Low-level input voltage        |          |     | 0.8 |      |     | 0.8 | V    |

| IOH | High-level output current      |          |     | -2  |      |     | -2  | mA   |

| IOL | Low-level output current       |          |     | 20  |      |     | 20  | mA   |

| TA  | Operating free-air temperature | -55      |     | 125 | 0    |     | 70  | °C   |

## electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| DADAMETED        | TERTO                             | ONDITIONS                | SN                 | SN54AS32 |      | SN74AS32           |      |      | UNIT |

|------------------|-----------------------------------|--------------------------|--------------------|----------|------|--------------------|------|------|------|

| PARAMETER        | TESTC                             | TEST CONDITIONS          |                    | түр‡     | MAX  | MIN                | TYP‡ | MAX  | UNIT |

| VIK              | V <sub>CC</sub> = 4.5 V,          | lj = -18 mA              |                    |          | -1.2 |                    |      | -1.2 | V    |

| VOH              | V <sub>CC</sub> = 4.5 V to 5.5 V, | $I_{OH} = -2 \text{ mA}$ | V <sub>CC</sub> -2 |          |      | V <sub>CC</sub> -2 | 2    |      | V    |

| VOL              | V <sub>CC</sub> = 4.5 V,          | I <sub>OL</sub> = 20 mA  |                    | 0.35     | 0.5  |                    | 0.35 | 0.5  | V    |

| lı               | V <sub>CC</sub> = 5.5 V,          | V <sub>I</sub> = 7 V     |                    |          | 0.1  |                    |      | 0.1  | mA   |

| IIН              | V <sub>CC</sub> = 5.5 V,          | V <sub>I</sub> = 2.7 V   |                    |          | 20   |                    |      | 20   | μΑ   |

| ١ <sub>١L</sub>  | V <sub>CC</sub> = 5.5 V,          | V <sub>I</sub> = 0.4 V   |                    |          | -0.5 |                    |      | -0.5 | mA   |

| ۱ <sub>О</sub> § | V <sub>CC</sub> = 5.5 V,          | V <sub>O</sub> = 2.25 V  | -30                |          | -112 | -30                |      | -112 | mA   |

| Іссн             | V <sub>CC</sub> = 5.5 V,          | VI = 4.5 V               |                    | 7.3      | 12   |                    | 7.3  | 12   | mA   |

| ICCL             | V <sub>CC</sub> = 5.5 V,          | V <b>I</b> = 0           |                    | 16.5     | 26.6 |                    | 16.5 | 26.6 | mA   |

<sup>‡</sup> All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> =  $25^{\circ}$ C.

§ The output conditions have been chosen to produce a current that closely approximates one half of the true short-circuit output current, IOS.

#### switching characteristics (see Figure 1)

| PARAMETER        | FROM<br>(INPUT) | то<br>(ОИТРИТ) | CL<br>RL<br>TA | V <sub>CC</sub> = 4.5 V to 5.5 V,<br>C <sub>L</sub> = 50 pF,<br>R <sub>L</sub> = 500 Ω,<br>T <sub>A</sub> = MIN to MAX <sup>¶</sup> |       | UNIT |     |

|------------------|-----------------|----------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------|-------|------|-----|

|                  |                 |                | SN54           | AS32                                                                                                                                | SN74/ | AS32 |     |

|                  |                 |                | MIN            | MAX                                                                                                                                 | MIN   | MAX  |     |

| <sup>t</sup> PLH | A or B          | v              | 1              | 7.5                                                                                                                                 | 1     | 5.8  | ns  |

| <sup>t</sup> PHL | AOIB            | I              | 1              | 6.5                                                                                                                                 | 1     | 5.8  | 115 |

For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

SDAS113B - APRIL 1982 - REVISED DECEMBER 1994

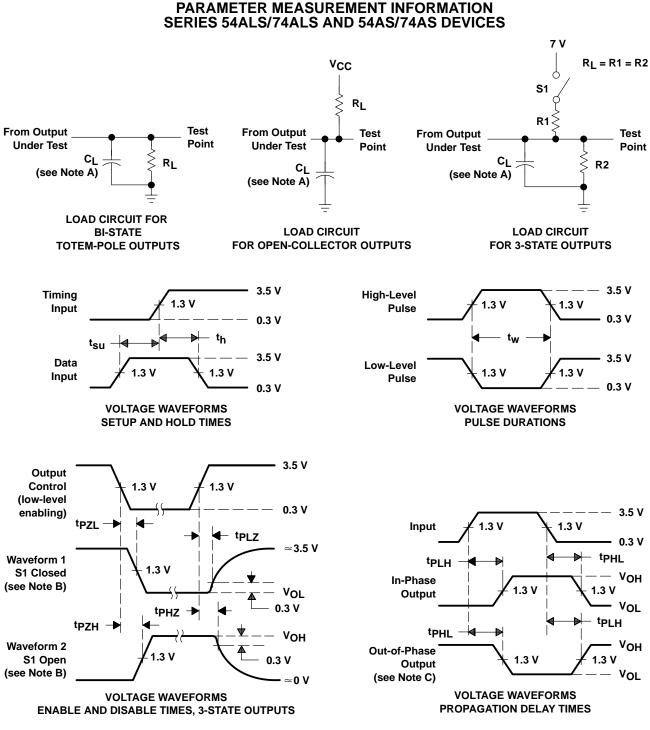

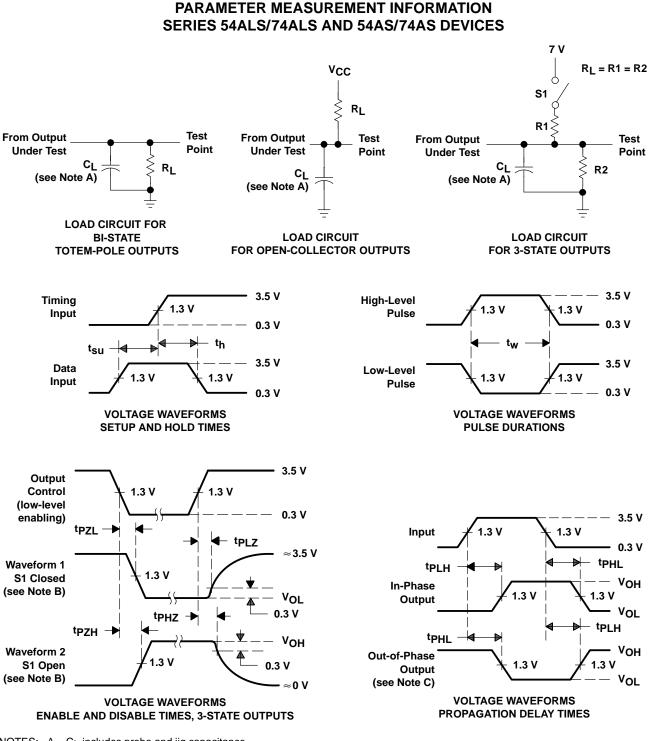

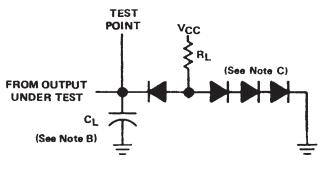

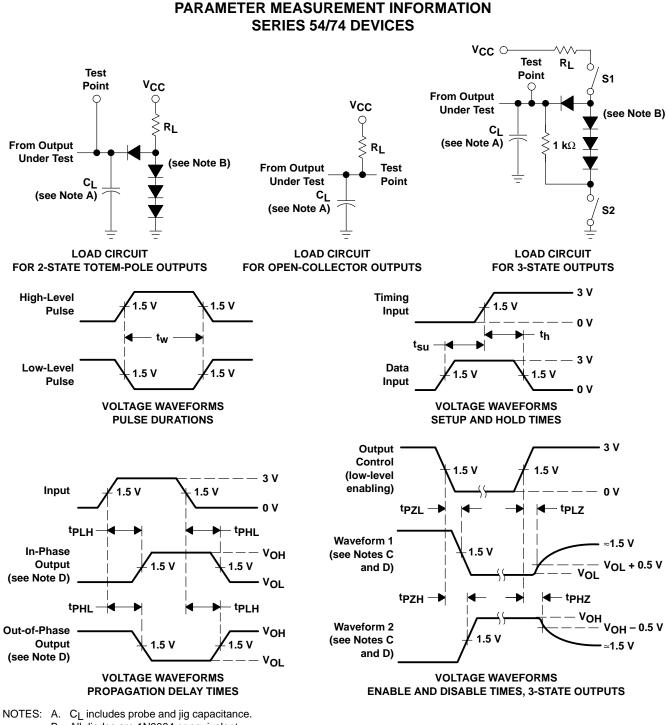

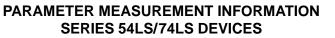

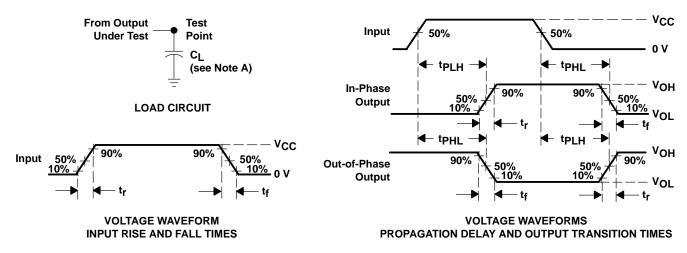

NOTES: A. CL includes probe and jig capacitance.

- B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

C. When measuring propagation delay items of 3-state outputs, switch S1 is open.

- D. All input pulses have the following characteristics: PRR  $\leq$  1 MHz, t<sub>r</sub> = t<sub>f</sub> = 2 ns, duty cycle = 50%.

- E. The outputs are measured one at a time with one transition per measurement.

#### Figure 1. Load Circuits and Voltage Waveforms

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1996, Texas Instruments Incorporated

## FAIRCHILD

SEMICONDUCTOR

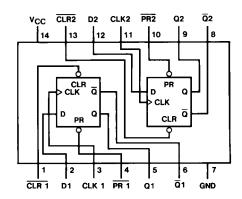

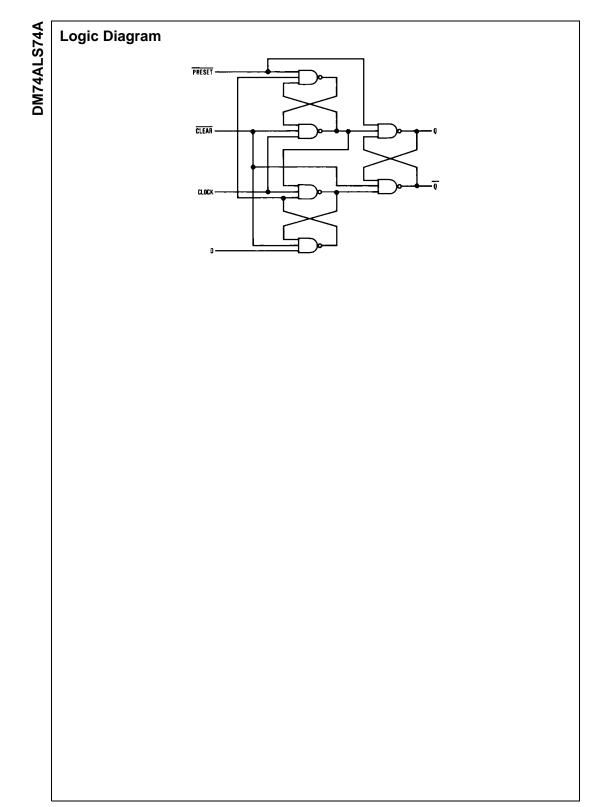

## DM74ALS74A Dual D Positive-Edge-Triggered Flip-Flop with Preset and Clear

#### **General Description**

The DM74ALS74A contains two independent positive edge-triggered flip-flops. Each flip-flop has individual D, clock, clear and preset inputs, and also complementary Q and  $\overline{\mathsf{Q}}$  outputs.

Information at input D is transferred to the Q output on the positive going edge of the clock pulse. Clock triggering occurs at a voltage level of the clock pulse and is not directly related to the transition time of the positive going pulse. When the clock input is at either the HIGH or LOW level, the D input signal has no effect.

Asynchronous preset and clear inputs will set or clear Q output respectively upon the application of low level signal.

#### Features

- Switching specifications at 50 pF

- Switching specifications guaranteed over full temperature and V<sub>CC</sub> range

September 1986

Revised February 2000

- Advanced oxide-isolated, ion-implanted Schottky TTL process

- Functionally and pin-for-pin compatible with Schottky and LS TTL counterpart

- Improved AC performance over LS74 at approximately half the power

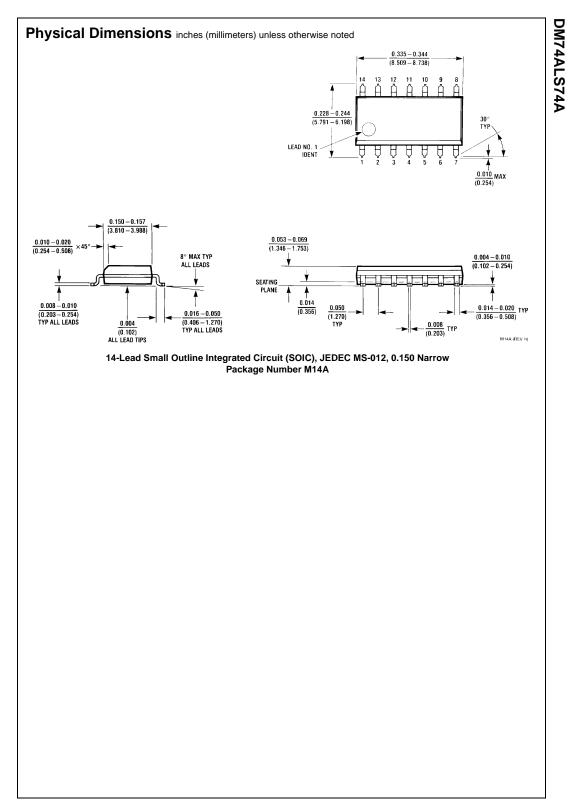

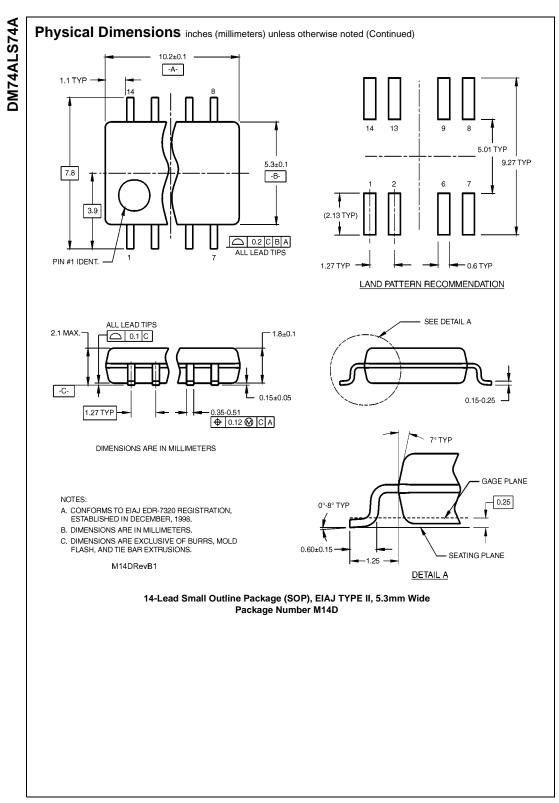

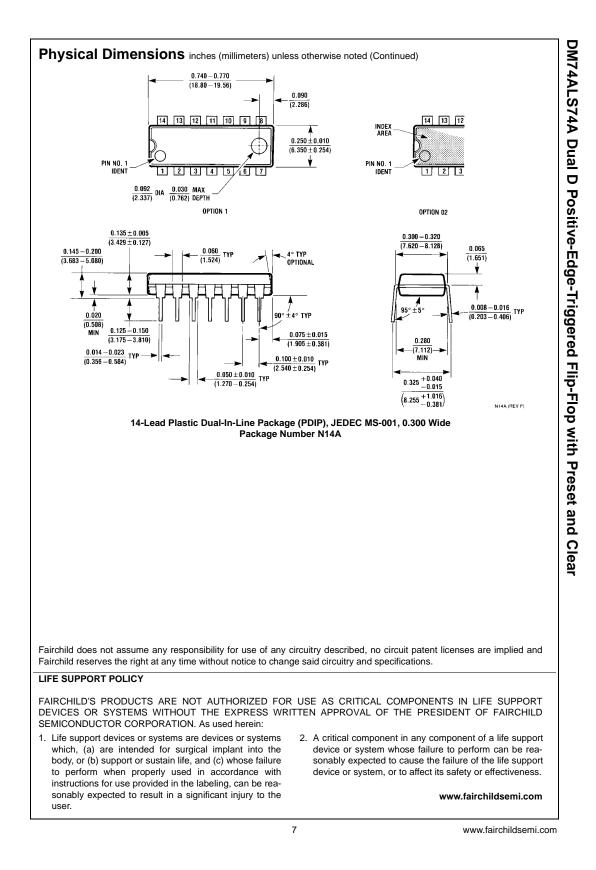

#### **Ordering Code:**

| Order Number | Package Number | Package Description                                                         | - |

|--------------|----------------|-----------------------------------------------------------------------------|---|

| DM74ALS74AM  | M14A           | 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow | - |

| DM74ALS74ASJ | M14D           | 14-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide               |   |

| DM74ALS74AN  | N14A           | 14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide       |   |

Devices also available in Tape and Reel. Specify by appending the suffix letter "X" to the ordering code.

#### **Connection Diagram**

# Function Table

| PR | CLR | CLK        | D | Q              | Q                |  |

|----|-----|------------|---|----------------|------------------|--|

| L  | Н   | Х          | Х | Н              | L                |  |

| н  | L   | Х          | Х | L              | Н                |  |

| L  | L   | Х          | Х | H (Note 1)     | H (Note 1)       |  |

| н  | н   | $\uparrow$ | Н | н              | L                |  |

| н  | н   | $\uparrow$ | L | L              | н                |  |

| н  | н   | L          | Х | Q <sub>0</sub> | $\overline{Q}_0$ |  |

Outputs

L = LOW State

H = HIGH State X = Don't Care

↑ = Positive Edge Transition

Q<sub>0</sub> = Previous Condition of Q

Note 1: This condition is nonstable; it will not persist when preset and clear inputs return to their inactive (HIGH) level. The output levels in this condition are not guaranteed to meet the  $V_{OH}$  specification.

© 2000 Fairchild Semiconductor Corporation DS006109

#### Absolute Maximum Ratings(Note 2)

| Supply Voltage                       | 7V                              |

|--------------------------------------|---------------------------------|

| Input Voltage                        | 7V                              |

| Operating Free Air Temperature Range | $0^{\circ}C$ to $+70^{\circ}C$  |

| Storage Temperature Range            | $-65^\circ C$ to $+150^\circ C$ |

| Typical θ <sub>JA</sub>              |                                 |

| N Package                            | 87.0°C/W                        |

| M Package                            | 117.0°C/W                       |

Note 2: The "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the absolute maximum ratings. The "Recommended Operating Conditions" table will define the conditions for actual device operation.

## **Recommended Operating Conditions**

| Symbol                                   | Pa                            | rameter                | Min          | Nom | Max  | Units |  |

|------------------------------------------|-------------------------------|------------------------|--------------|-----|------|-------|--|

| V <sub>CC</sub>                          | Supply Voltage                |                        | 4.5          | 5   | 5.5  | V     |  |

| VIH                                      | HIGH Level Input Voltage      |                        | 2            |     |      | V     |  |

| VIL                                      | LOW Level Input Voltage       |                        |              |     | 0.8  | V     |  |

| I <sub>OH</sub>                          | HIGH Level Output Current     |                        |              |     | -0.4 | mA    |  |

| I <sub>OL</sub>                          | LOW Level Output Current      |                        |              |     | 8    | mA    |  |

| f <sub>CLK</sub>                         | Clock Frequency               |                        | 0            |     | 34   | MHz   |  |

| t <sub>W(CLK)</sub> Width of Clock Pulse | Width of Clock Pulse          | HIGH                   | 14.5         |     |      | ns    |  |

|                                          |                               | LOW                    | 14.5         |     |      | ns    |  |

| t <sub>W</sub>                           | Pulse Width<br>Preset & Clear | LOW                    | 14.5         |     |      | ns    |  |

| t <sub>SU</sub>                          | Data Setup Time               | Data                   | 15↑ (Note 3) |     | -    |       |  |

|                                          |                               | PRE or CLR<br>Inactive | 10↑ (Note 3) |     |      | ns    |  |

| t <sub>H</sub>                           | Data Hold Time                | •                      | 0↑ (Note 3)  |     |      | ns    |  |

| T <sub>A</sub>                           | Free Air Operating Temp       | erature                | 0            |     | 70   | °C    |  |

Note 3: The  $(\uparrow)$  arrow indicates the positive edge of the Clock is used for reference.

#### **Electrical Characteristics**

over recommended operating free air temperature range. All typical values are measured at  $V_{CC}$  = 5V,  $T_A$  = 25°C.

| Symbol          | Parameter            | Conditions                      |                                       | Min                 | Тур  | Max  | Units |

|-----------------|----------------------|---------------------------------|---------------------------------------|---------------------|------|------|-------|

| V <sub>IK</sub> | Input Clamp Voltage  | $V_{CC} = 4.5 V, I_I = -18$     | $V_{CC} = 4.5V, I_I = -18 \text{ mA}$ |                     |      | -1.5 | V     |

| V <sub>OH</sub> | HIGH Level           | I <sub>OH</sub> = -0.4 mA       |                                       | V 0                 |      |      |       |

|                 | Output Voltage       | $V_{CC} = 4.5 V$ to $5.5 V$     |                                       | V <sub>CC</sub> – 2 |      |      | V     |

| V <sub>OL</sub> | LOW Level            | $V_{CC} = 4.5V$                 | I <sub>OL</sub> = 8 mA                |                     | 0.35 | 0.5  | V     |

|                 | Output Voltage       | $V_{IH} = 2V$                   | IOL = 0 IIIA                          |                     | 0.55 | 0.5  | v     |

| l <sub>l</sub>  | Input Current @      | $V_{CC} = 5.5V,$                | Clock, D                              |                     |      | 0.1  | mA    |

|                 | Max Input Voltage    | $V_{IH} = 7V$                   | Preset, Clear                         |                     |      | 0.2  | IIIA  |

| I <sub>IH</sub> | HIGH Level           | $V_{CC} = 5.5V,$                | Clock, D                              |                     |      | 20   | A     |

|                 | Input Current        | $V_{IH} = 2.7V$                 | Preset, Clear                         |                     |      | 40   | μA    |

| IIL             | LOW Level            | V <sub>CC</sub> = 5.5V,         | Clock, D                              |                     |      | -0.2 |       |

|                 | Input Current        | $V_{IL} = 0.4V$                 | Preset, Clear (Note 5)                |                     |      | -0.4 | mA    |

| I <sub>O</sub>  | Output Drive Current | $V_{CC} = 5.5V, V_{O} = 2.$     | 25V                                   | -30                 |      | -112 | mA    |

| I <sub>CC</sub> | Supply Current       | V <sub>CC</sub> = 5.5V (Note 4) |                                       |                     | 2.4  | 4    | mA    |

**Note 5:** I<sub>IL</sub> PRE and CLR pins not guaranteed to meet specifications with both PRE and CLK LOW.

### **Switching Characteristics**

over recommended operating free air temperature range.

| Parameter        | Conditions              | From             | То     | Min | Max | Units |

|------------------|-------------------------|------------------|--------|-----|-----|-------|

| f <sub>MAX</sub> | $V_{CC} = 4.5V$ to 5.5V |                  |        | 34  |     | MHz   |

| t <sub>PLH</sub> | $R_L = 500\Omega$       | Preset or Clear  | Q or Q | 3   | 13  | ns    |

| t <sub>PHL</sub> | $C_L = 50 \text{ pF}$   | Treaser of Olean | a la   | 5   | 15  | ns    |

| t <sub>PLH</sub> |                         | Clock            | Q or Q | 5   | 16  | ns    |

| t <sub>PHL</sub> |                         | CIUCK            | 90102  | 5   | 18  | ns    |

- Package Options Include Plastic and Ceramic DIPs and Ceramic Flat Packages

- Dependable Texas Instruments Quality and Reliability

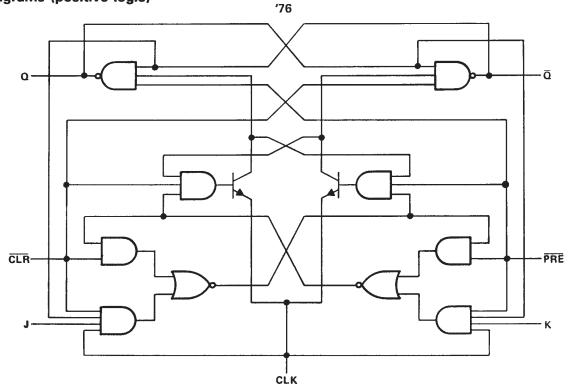

#### description

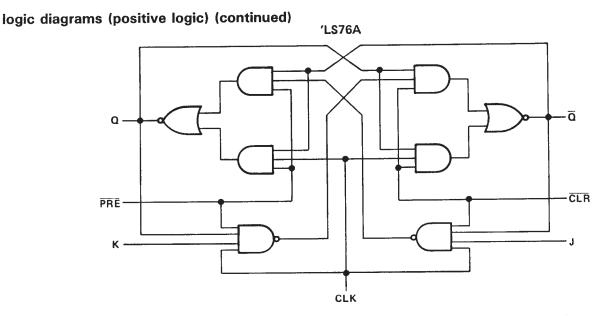

The '76 contains two independent J-K flip-flops with individual J-K, clock, preset, and clear inputs. The '76 is a positive-edge-triggered flipflop. J-K input is loaded into the master while the clock is high and transferred to the slave on the high-to-low transition. For these devices the J and K inputs must be stable while the clock is high.

The 'LS76A contain two independent negativeedge-triggered flip-flops. The J and K inputs must be stable one setup time prior to the highto-low clock transition for predicatble operation. The preset and clear are asynchronous active low inputs. When low they override the clock and data inputs forcing the outputs to the steady state levels as shown in the function table.

The SN5476 and the SN54LS76A are characterized for operation over the full military temperature range of -55 °C to 125 °C. The SN7476 and the SN74LS76A are characterized for operation from 0 °C to 70 °C.

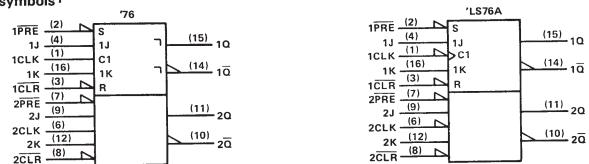

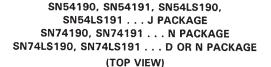

SN5476, SN54LS76A . . . J PACKAGE SN7476 . . . N PACKAGE SN74LS76A . . . D OR N PACKAGE (TOP VIEW)

| 1 CLK    1    16    1K      1 PRE    2    15    1Q      1 CLR    3    14    1Q      1 J    4    13    GND      VCC    5    12    2K      2CLK    6    11    2Q      2 PRE    7    10    2Q      2 CLR    8    9    2J |                                                |                  |                | ,                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|------------------|----------------|-------------------------------------------------------|

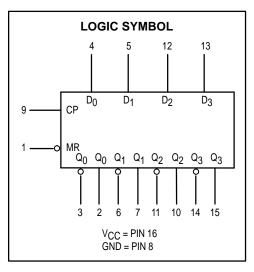

|                                                                                                                                                                                                                       | 1 PRE<br>1 CLR<br>1 J<br>VCC<br>2 CLK<br>2 PRE | -<br>3<br>4<br>5 | 15<br>14<br>13 | ] 10<br>] 10<br>] GND<br>] 2К<br>] 20<br>] 20<br>] 20 |