## Estructura de Computadores

### El computador simple

Autores: David Guerrero. Isabel Gómez, Alberto Molina

Usted es libre de copiar, distribuir y comunicar públicamente la obra y de hacer obras derivadas siempre que se cite la fuente y se respeten las condiciones de la licencia Attribution-Share alike de Creative Commons.

Texto completo de la licencia: http://creativecommons.org/licenses/by-nc-sa/3.0/es/

## Guión

- ▶ El punto de partida: La calculadora

- Automatización en la ejecución

- Almacenamiento de los datos

- Diversificación de instrucciones

- Una posible implementación

- Ejemplos de uso

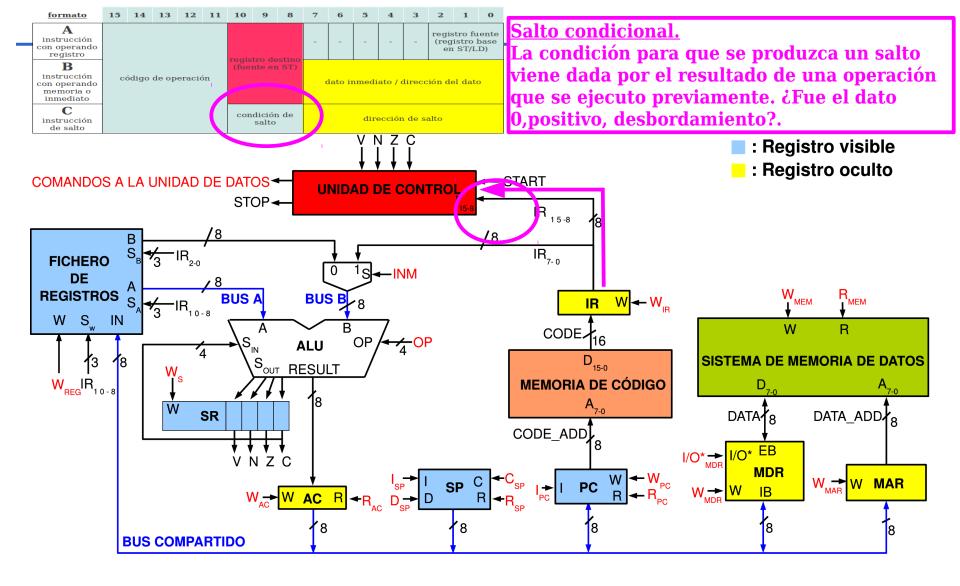

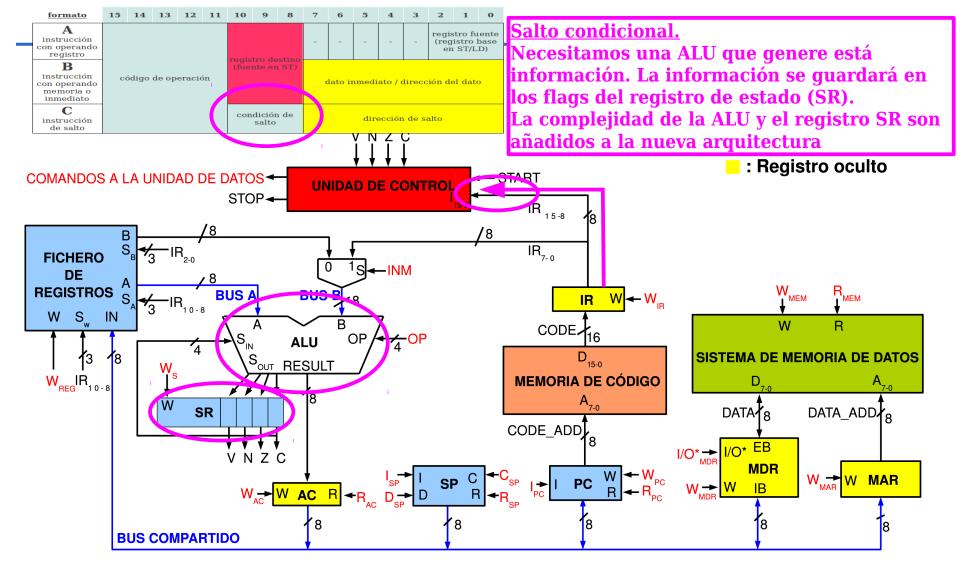

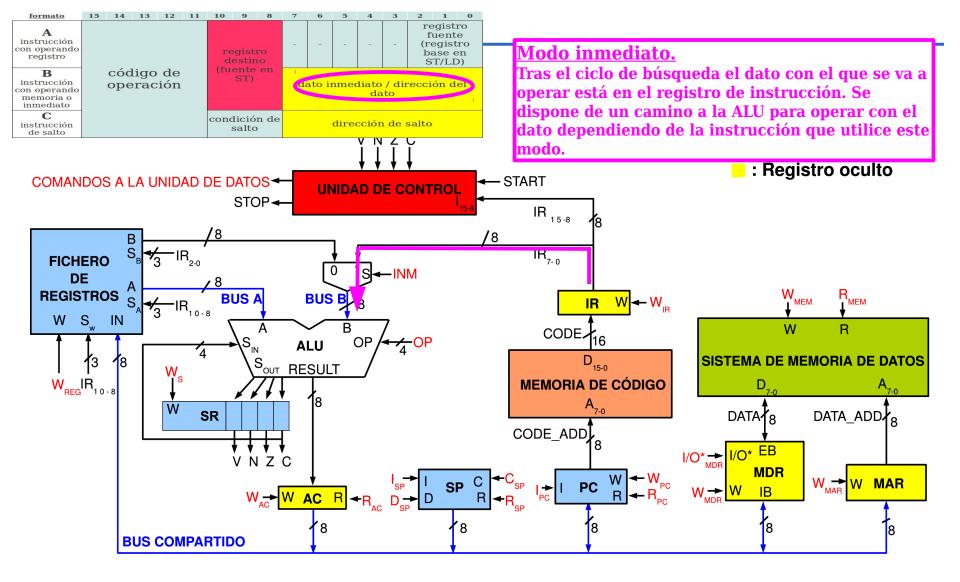

- El computador simple 2 presenta muchas deficiencias: imposibilidad de realizar saltos en la ejecución del programa, ausencia de variables de estado que informen del resultado de las operaciones, imposibilidad de usar inmediatos falta de comunicación con el exterior...

- Se propone una arquitectura pensada para solventar estas deficiencias: el CS2010.

- Se ha procurado que la arquitectura del CS2010 sea similar a la del microcontrolador que veremos en el tema siguiente, aunque muchísimo más simple.

#### Modelo de usuario: registros visibles

- Todos los registros visibles son de 8 bits

- Los de propósito general se etiquetan R0, R1, R2, R3, R4, R5, R6 y R7.

- Los de propósito específico son los siguientes:

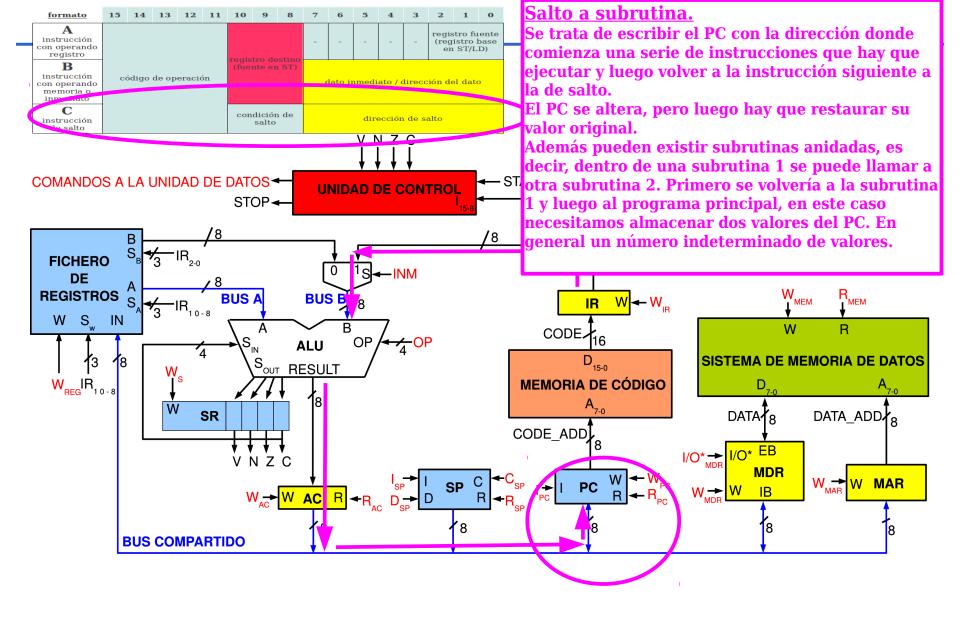

- **PC o contador de programa:** Contiene la dirección de la próxima instrucción que se ejecutará. Se inicializa a cero y se va incrementando a medida que se ejecutan las instrucciones.

- SR o registro de estado: Sus bits útiles se etiquetan Z (cero), V (desbordamiento), N (negativo) y C (carry). Indican, respectivamente, si la última instrucción aritmética/lógica generó un resultado con todos los bits a cero, un resultado no representable en complemento a 2, un resultado que es negativo al interpretarlo en complemento a 2 o si provocó carry/borrow.

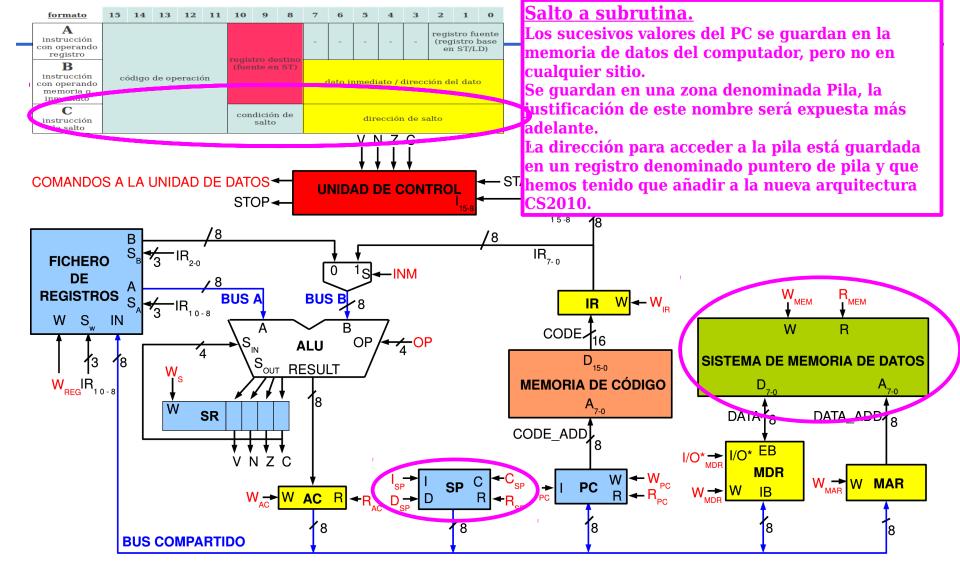

- SP o puntero de pila: Sirve para implementar la estructura de pila en memoria. Codifíca la dirección de la primera posición libre. El puntero de pila se va decrementando a medida que se apilan datos y se incrementa al desapilarlos. Estos incrementos y decrementos se hacen de forma automatizada al realizar llamadas y retornos de subrutina.

#### Modelo de usuario: ISP

- Se pretende que el juego de instrucciones ensamblador del CS2010 sea básicamente un subconjunto muy reducido del de la arquitectura AVR.

- Esto no implica que el formato del código máquina en ambos sistemas sea similar: El formato de instrucciones del CS2010 es muchísimo más simple.

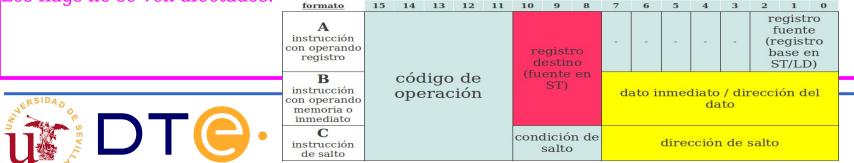

- Se usará un código de operación de longitud fija, 5 bits, lo que permite disponer un máximo de 32 códigos de operación.

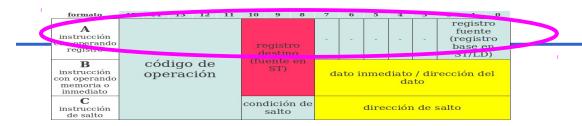

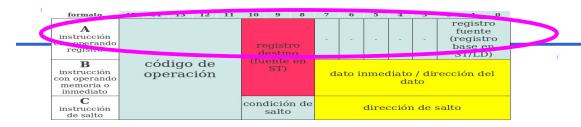

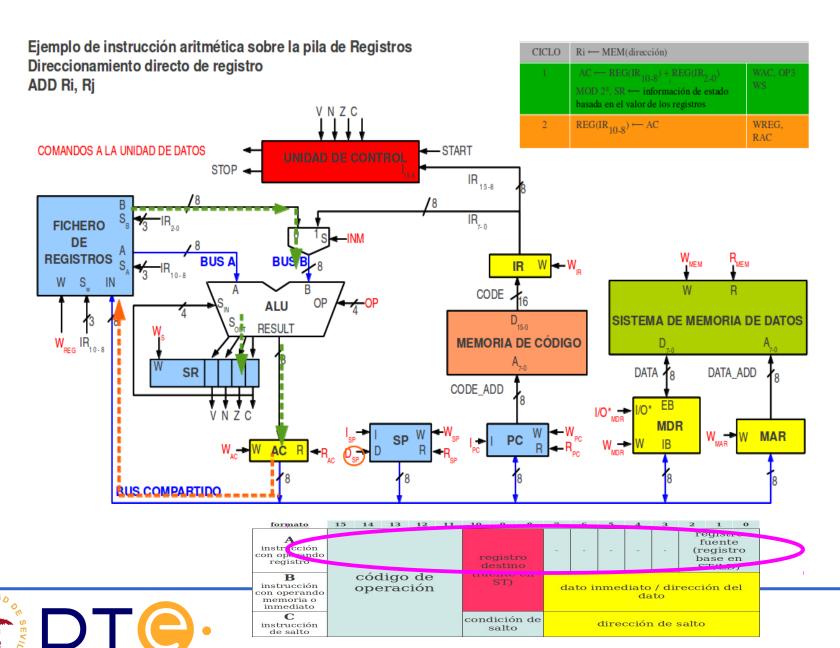

Formatos: Solo hay tres y comparten campos

| <u>formato</u>                                                                      | 15 | 14    | 13    | 12     | 11  | 10              | 9                | 8 | 7 | 6            | 5          | 4       | 3           | 2          | 1                          | 0          |

|-------------------------------------------------------------------------------------|----|-------|-------|--------|-----|-----------------|------------------|---|---|--------------|------------|---------|-------------|------------|----------------------------|------------|

| A instrucción con operando registro  B instrucción con operando memoria o inmediato | CÓ | ódigo | de op | eracić | ón  |                 | tro de<br>nte en |   | - | -<br>dato in | -<br>nmedi | ato / d | -<br>direcc | (reg<br>en | stro fu<br>istro l<br>ST/L | base<br>D) |

| C<br>instrucción<br>de salto                                                        |    |       |       |        | con | diciór<br>salto | ı de             |   |   | dire         | ección     | ı de sa | alto        |            |                            |            |

## Diversificación de instrucciones Asignación de códigos de operación: Facilita la decodificación

| Bits del código<br>de operación |    |    |   |   | NEMÓNICO     | FORMATO | TIPO                | SINTAXIS               | EFECTO <sup>1</sup>              | VNZC <sup>2</sup> |

|---------------------------------|----|----|---|---|--------------|---------|---------------------|------------------------|----------------------------------|-------------------|

| 15                              | 14 | 13 |   |   |              |         |                     |                        |                                  |                   |

| 0                               | 0  | 0  | 0 | 0 | ST           | Α       | memoria             | ST (Rbase),Rfuente     | MEM[Rbase]←Rfuente               |                   |

| 0                               | 0  | 0  | 0 | 1 | LD           | Α       | memoria             | LD Rdestino,(Rbase)    | Rdestino←MEM[Rbase]              |                   |

| 0                               | 0  | 0  | 1 | 0 | STS          | В       | memoria             | STS dirección,Rfuente  | MEM[dirección]← <b>Rfuente</b>   |                   |

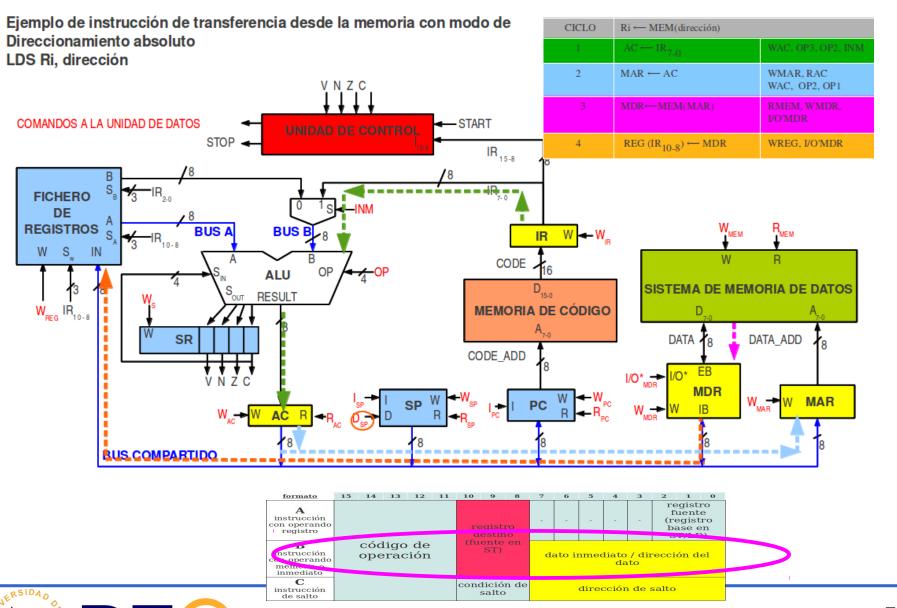

| 0                               | 0  | 0  | 1 | 1 | LDS          | В       | memoria             | LDS Rdestino,dirección | Rdestino←MEM[dirección]          |                   |

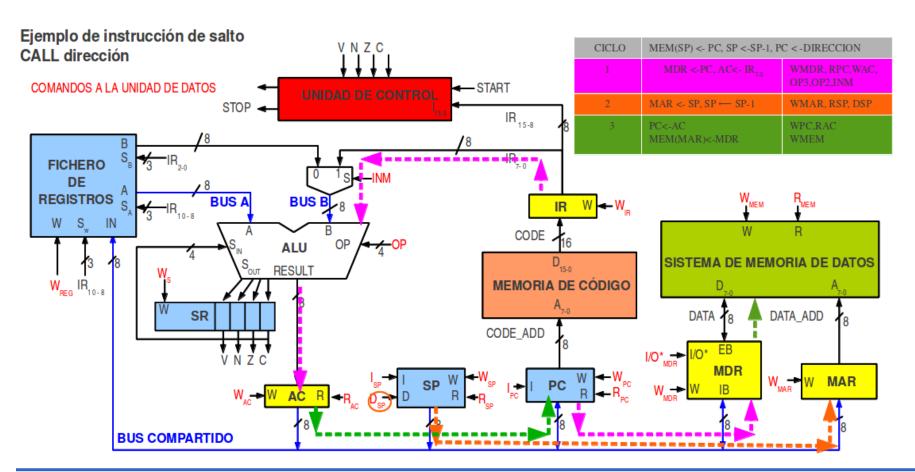

| 0                               | 0  | 1  | 0 | 0 | CALL         | С       | salto               | CALL dirección         | MEM[SP]←PC,SP←SP-1, PC←dirección |                   |

| 0                               | 0  | 1  | 0 | 1 | RET          | -       | salto               | RET                    | PC←MEM[SP+1],SP←SP+1             |                   |

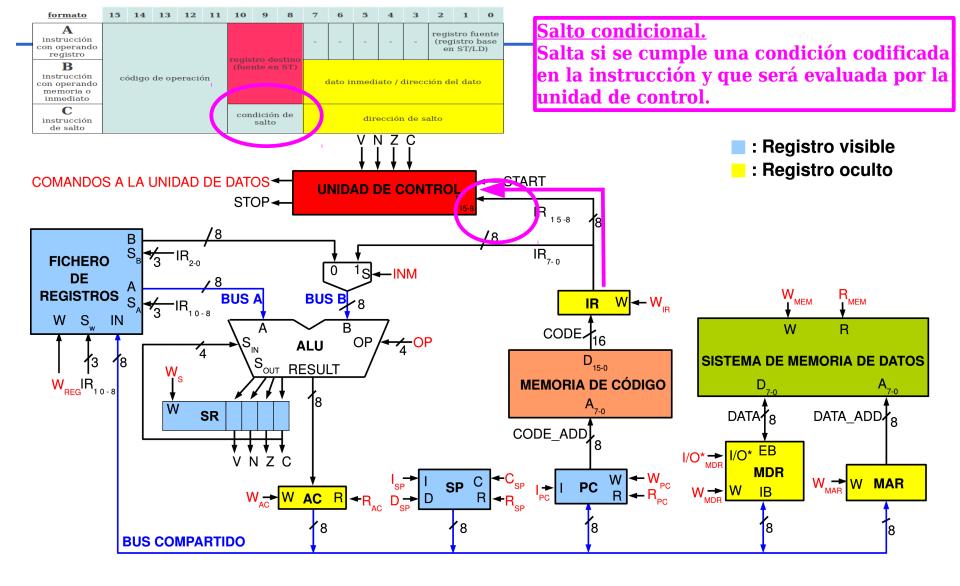

| 0                               | 0  | 1  | 1 | 0 | BR <i>xx</i> | С       | salto               | BR <i>xx</i> dirección | xx: PC←dirección                 |                   |

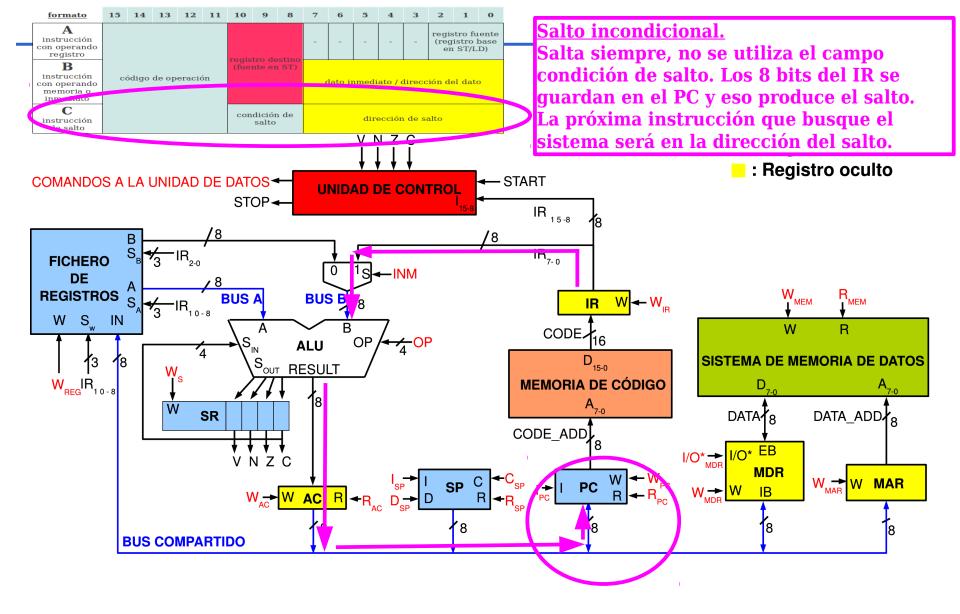

| 0                               | 0  | 1  | 1 | 1 | JMP          | С       | salto               | JMP dirección          | PC←dirección                     |                   |

| 0                               | 1  | 0  | 0 | 0 | ADD          | Α       | aritmético/lógica   | ADD Rdestino,Rfuente   | Rdestino←Rdestino+Rfuente        | ****              |

| 0                               | 1  | 0  | 0 | 1 | -            | -       | -                   | -                      | no documentado                   | UUUU              |

| 0                               | 1  | 0  | 1 | 0 | SUB          | Α       | aritmético/lógica   | SUB Rdestino,Rfuente   | Rdestino←Rdestino-Rfuente        | ****              |

| 0                               | 1  | 0  | 1 | 1 | СР           | Α       | estado              | CP Rdestino,Rfuente    | NOP                              | ****              |

| 0                               | 1  | 1  | 0 | 0 | -            | -       | -                   | -                      | no documentado                   | UUUU              |

| 0                               | 1  | 1  | 0 | 1 | -            | -       | -                   | -                      | no documentado                   | UUUU              |

| 0                               | 1  | 1  | 1 | 0 | =            | -       | =                   | -                      | no documentado                   | UUUU              |

| 0                               | 1  | 1  | 1 | 1 | MOV          | Α       | movimiento de datos | MOV Rdestino,Rfuente   | Rdestino←Rfuente                 |                   |

| 1                               | 0  | 0  | 0 | 0 | =            | -       | =                   | -                      | no documentado                   | UUUU              |

| 1                               | 0  | 0  | 0 | 1 | -            | -       | -                   | -                      | no documentado                   | UUUU              |

| 1                               | 0  | 0  | 1 | 0 | CLC          | -       | estado              | CLC                    | NOP                              | *                 |

| 1                               | 0  | 0  | 1 | 1 | SEC          | -       | estado              | SEC                    | NOP                              | *                 |

| 1                               | 0  | 1  | 0 | 0 | ROR          | AoB     | desplazamiento      | ROR Rdestino           | Rdestino←SHR(Rdestino,C)         | ****              |

| 1                               | 0  | 1  | 0 | 1 | ROL          | AoB     | desplazamiento      | ROL Rdestino           | Rdestino←SHL(Rdestino,C)         | ****              |

| 1                               | 0  | 1  | 1 | 0 | -            | -       | -                   | -                      | no documentado                   | UUUU              |

| 1                               | 0  | 1  | 1 | 1 | STOP         | -       | especial            | STOP                   | lleva el procesador a espera     |                   |

| 1                               | 1  | 0  | 0 | 0 | ADDI         | В       | aritmético/lógica   | ADDI Rdestino,dato     | Rdestino←Rdestino+dato           | ****              |

| 1                               | 1  | 0  | 0 | 1 | -            | -       | -                   | -                      | no documentado                   | UUUU              |

| 1                               | 1  | 0  | 1 | 0 | SUBI         | В       | aritmético/lógica   | SUBI Rdestino,dato     | Rdestino←Rdestino-dato           | ****              |

| 1                               | 1  | 0  | 1 | 1 | CPI          | В       | estado              | CPI Rdestino,dato      | NOP                              | ****              |

| 1                               | 1  | 1  | 0 | 0 | =            | -       | -                   | -                      | no documentado                   | UUUU              |

| 1                               | 1  | 1  | 0 | 1 | -            | -       | -                   | -                      | no documentado                   | UUUU              |

| 1                               | 1  | 1  | 1 | 0 | =            | -       | -                   | -                      | no documentado                   | UUUU              |

| 1                               | 1  | 1  | 1 | 1 | LDI          | В       | movimiento de datos | LDI Rdestino,dato      | Rdestino←dato                    |                   |

<sup>&</sup>lt;sup>1</sup> (sin tener en cuenta el registro de estado y el incremento del PC)

<sup>&</sup>lt;sup>2</sup> El caracter '-' denota "no modificado", '\*' denota "modificado de forma definida", 'U' denota "no documentado"

Códigos de condición de la instrucción de bifurcación condicional: BRXX Los bits  $I_{10}I_{9}I_{8}$  codifican la condición de salto XX.

| I <sub>10</sub> | l <sub>9</sub> | <b>I</b> <sub>8</sub> | CONDICIÓN | nemónico(s)<br>de la condición | notas                                                                                                        |

|-----------------|----------------|-----------------------|-----------|--------------------------------|--------------------------------------------------------------------------------------------------------------|

| 0               | 0              | 0                     | Z         | ZS, EQ                         | será cierta justo tras realizar la resta A-B si y solo si A=B                                                |

| 0               | 0              | 1                     | С         | CS, LO                         | será cierta justo tras realizar la resta A-B si y solo si A <b<br>asumiendo notación base 2 sin signo</b<br> |

| 0               | 1              | 0                     | V         | VS                             | será cierta si y solo si el dato recién calculado no es<br>representable en notación complemento a 2         |

| 0               | 1              | 1                     | N xor V   | LT                             | será cierta justo tras realizar la resta A-B si y solo si A <b<br>asumiendo notación complemento a 2</b<br>  |

| 1               | -              | -                     | ?         | -                              | estas condiciones no están definidas y no deben utilizarse                                                   |

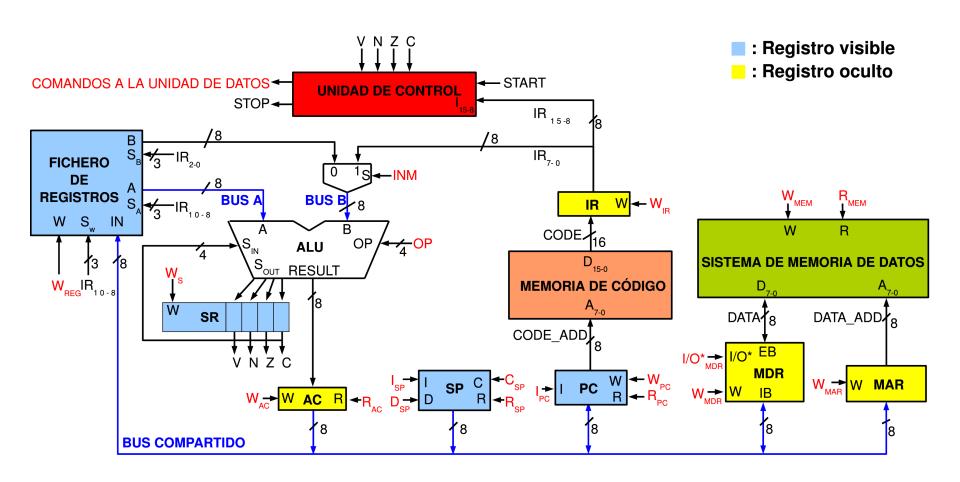

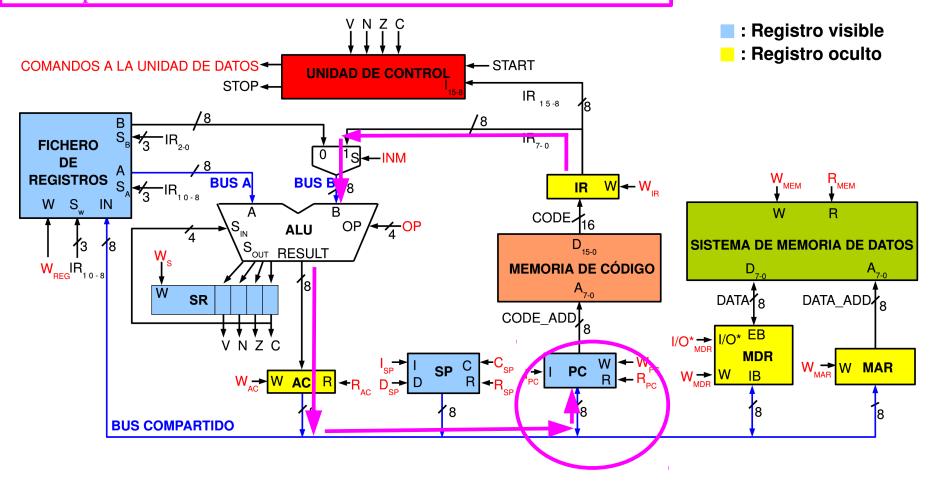

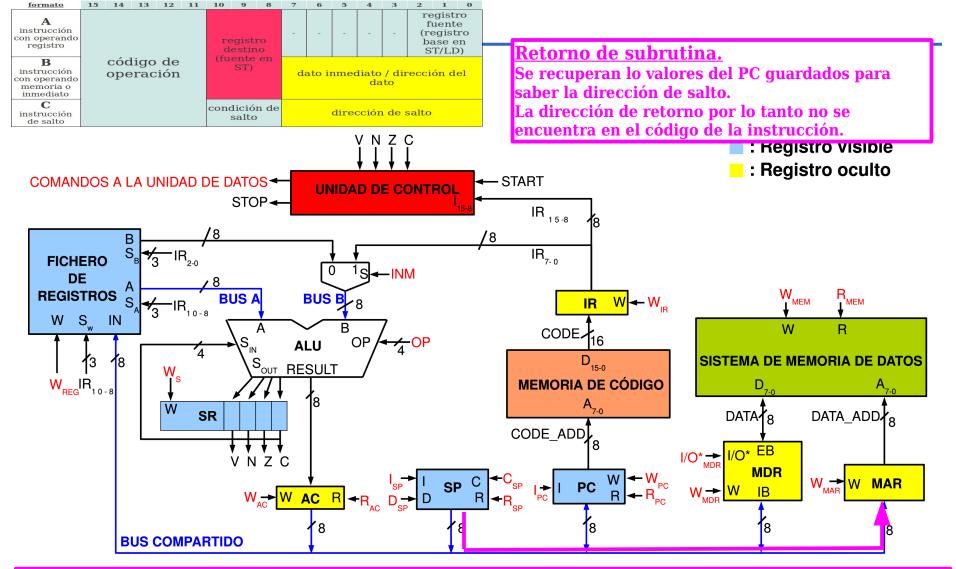

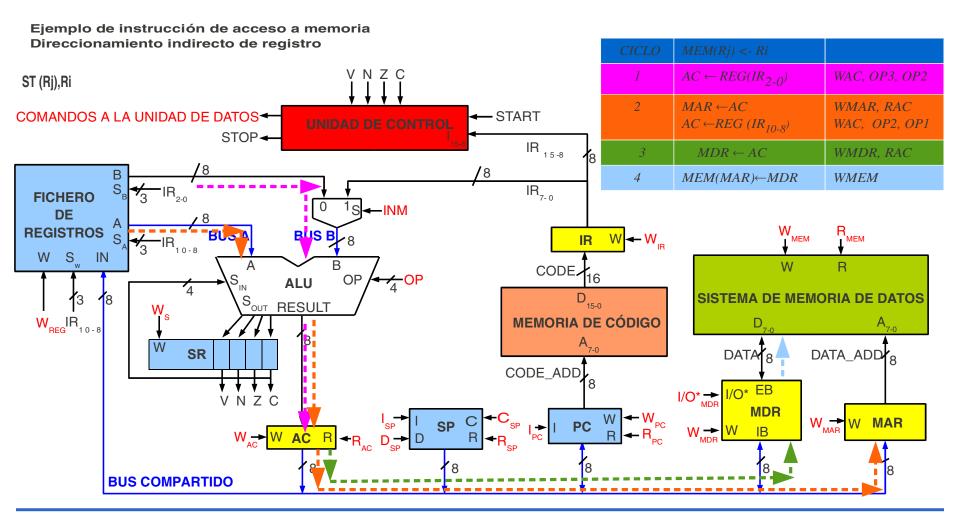

## Una posible implementación

## Una posible implementación

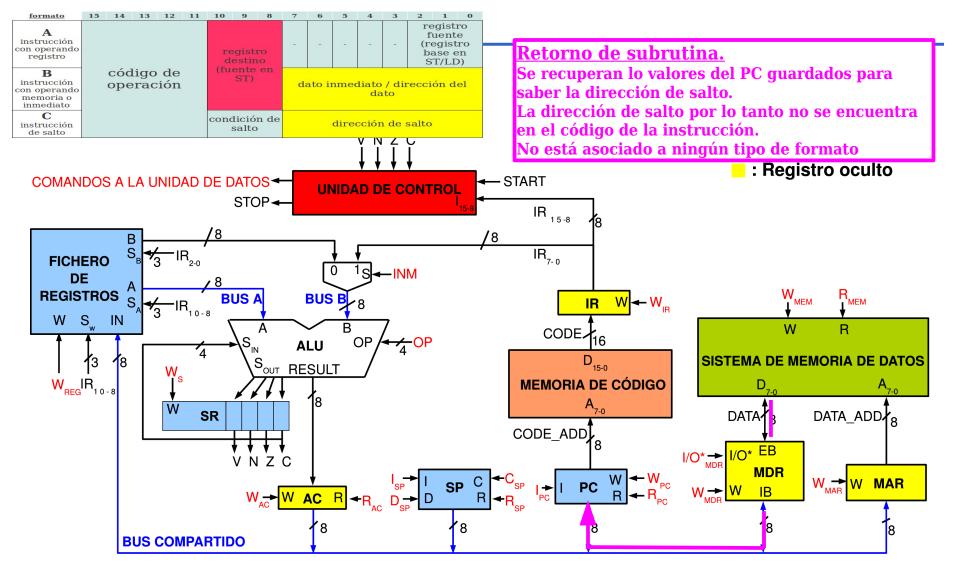

#### Registros ocultos

- ▶ IR: registro de 16 bits que sirve para almacenar la instrucción que está siendo ejecutada.

- ▶ MDR. Registro de 8 bits que sirve para almacenar los datos que se van a intercambiar con la memoria de datos.

- ▶ MAR. Registro de 8 bits que direcciona la memoria de datos.

- ▶ AC. Registro de 8 bits para almacenar temporalmente el resultado de la ALU

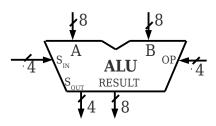

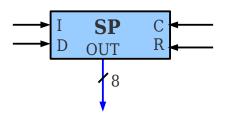

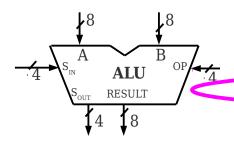

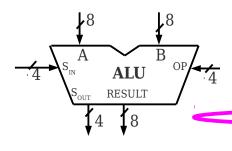

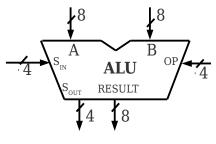

## Una posible implementación Descripción RT de los nuevos componentes

| $S_{IN} = \{V_{IN},$                                                 | , N <sub>IN</sub> , | Ζ <sub>IN</sub> , | $C_{IN}$           |

|----------------------------------------------------------------------|---------------------|-------------------|--------------------|

| $\boldsymbol{S}_{\text{out}} \!\!=\! \{\boldsymbol{V}_{\text{out'}}$ | $N_{\text{out'}}$   | Zou               | $_{T}$ , $C_{OUT}$ |

| OP <sub>3</sub> | OP <sub>2</sub> | OP <sub>1</sub> | OP <sub>0</sub> | RESULT=                    | V <sub>out</sub> =                  | N <sub>out</sub> =  | Z <sub>out</sub> =             | C <sub>out</sub> = |

|-----------------|-----------------|-----------------|-----------------|----------------------------|-------------------------------------|---------------------|--------------------------------|--------------------|

| 0               | 0               | -               | 0               | -                          | V <sub>IN</sub>                     | N <sub>IN</sub>     | Z <sub>IN</sub>                | Θ                  |

| 0               | 0               | 0               | 1               | -                          | -                                   | ı                   | -                              | -                  |

| 0               | 0               | 1               | 1               | -                          | V <sub>IN</sub>                     | N <sub>IN</sub>     | Z <sub>IN</sub>                | 1                  |

| 0               | 1               | 0               | 0               | SHR(A,C <sub>IN</sub> )    | C <sub>IN</sub> EXOR A <sub>0</sub> | RESULT <sub>7</sub> | NOT $OR_{i=0}^{7}(RESULT_{i})$ | A <sub>o</sub>     |

| 0               | 1               | 0               | 1               | SHL(A,C <sub>IN</sub> )    | A, EXOR A <sub>6</sub>              | RESULT,             | NOT $OR_{i=0}^{7}(RESULT_{i})$ | A <sub>7</sub>     |

| 0               | 1               | 1               | -               | Α                          | -                                   | -                   | -                              | -                  |

| 1               | 0               | 0               | -               | $(A + B) \mod 2^8$         | overflow(A+B)                       | RESULT <sub>7</sub> | NOT $OR_{i=0}^{7}(RESULT_{i})$ | carry(A+B)         |

| 1               | 0               | 1               | -               | (A - B) mod 2 <sup>8</sup> | underflow(A-B)                      | RESULT,             | NOT $OR_{i=0}^{7}(RESULT_{i})$ | borrow(A-B)        |

| 1               | 1               | -               | -               | В                          | -                                   | -                   | -                              | -                  |

| R | OUT:= |

|---|-------|

| 0 | HI    |

| 1 | SP    |

| I D C | SP ←       |

|-------|------------|

| 000   | SP         |

| 0 0 1 | 0          |

| 0 1 0 | SP-1       |

| 1 0 0 | SP+1       |

| OTRAS | PROHIBIDAS |

La descripción de SR es idéntica a la del MAR

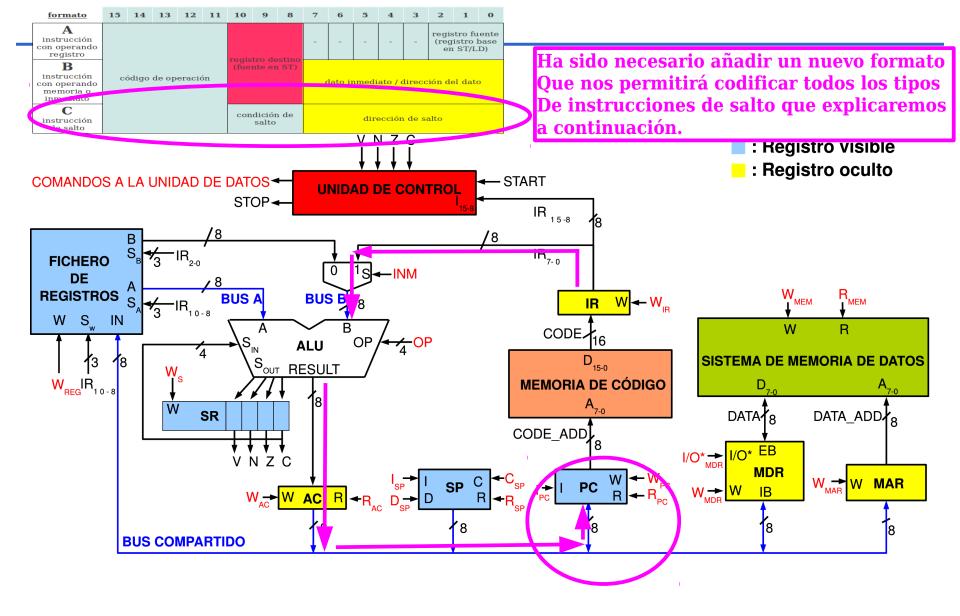

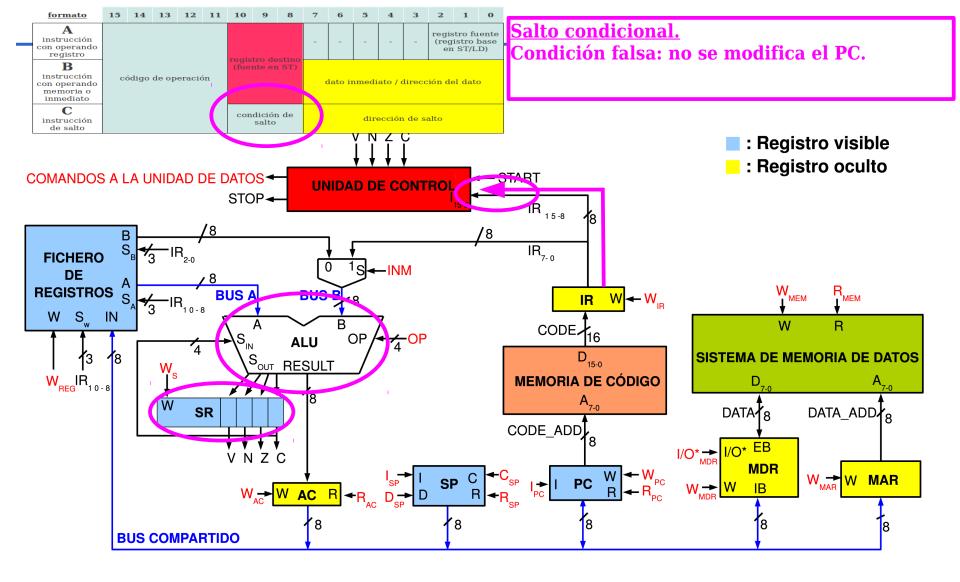

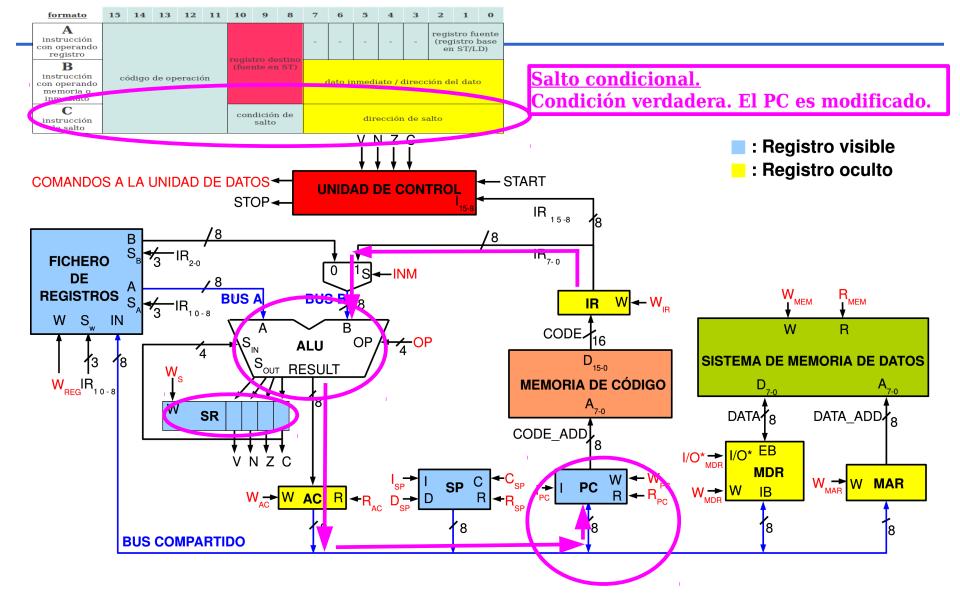

## Modificaciones en la arquitectura y el formato de instrucción que nos permiten añadir instrucciones de salto

¿Cómo se hace el salto?: en el PC, ya no cambia siempre de forma secuencial, se debe actualizar a la dirección del salto. ¿Dónde está la dirección del salto?: guardada en el código de la instrucción. El sistema debe de permitir guardar este dato en el PC. Necesitamos conectar el PC al bus para establecer un camino desde IR.

#### Información de lo que significan los códigos de condición

| ſ  |   |                       |                |           |                 |                                                                             |

|----|---|-----------------------|----------------|-----------|-----------------|-----------------------------------------------------------------------------|

|    |   |                       |                |           | nemónico(s)     |                                                                             |

|    |   | <b>I</b> <sub>9</sub> | I <sub>8</sub> | CONDICIÓN | de la condición | notas                                                                       |

|    | 0 | 0                     | 0              | Z         | ZS, EQ          | será cierta justo tras realizar la resta A-B si y solo si A=B               |

| _/ |   |                       |                |           |                 | será cierta justo tras realizar la resta A-B si y solo si A <b< td=""></b<> |

|    | 0 | 0                     | 1              | С         | CS, LO          | asumiendo notación base 2 sin signo                                         |

|    |   |                       |                |           |                 | será cierta si y solo si el dato recién calculado no es                     |

|    | 0 | 1                     | 0              | V         | VS              | representable en notación complemento a 2                                   |

| 1  |   |                       |                |           |                 | será cierta justo tras realizar la resta A-B si y solo si A <b< td=""></b<> |

|    | 0 | 1                     | 1              | N xor V   | LT              | asumiendo notación complemento a 2                                          |

|    | 1 | -                     | -              | ?         | _               | estas condiciones no están definidas y no deben utilizarse                  |

| ,  |   |                       |                |           | <del>/</del>    |                                                                             |

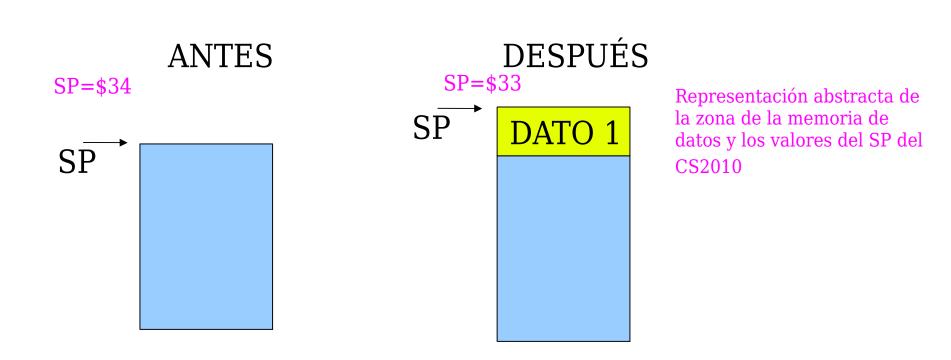

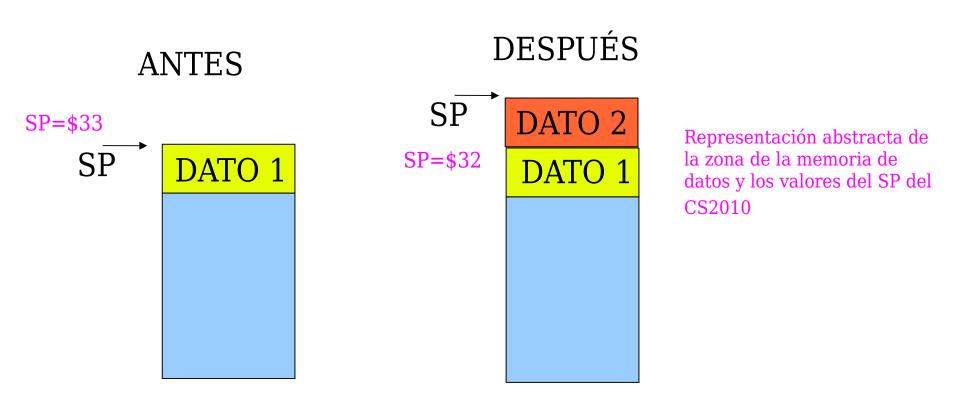

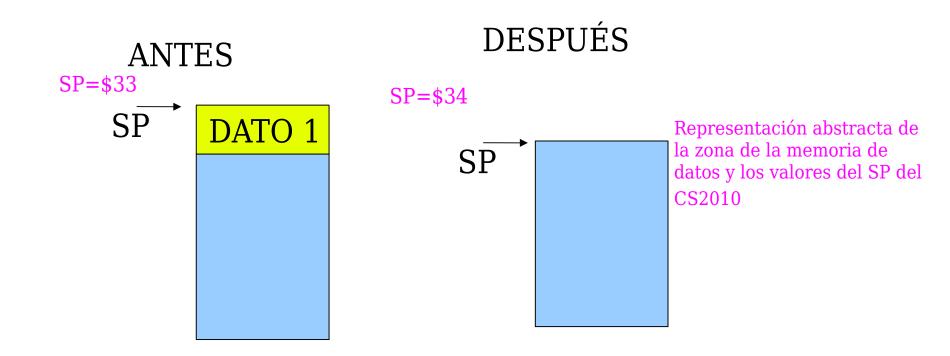

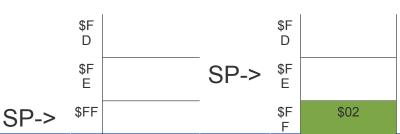

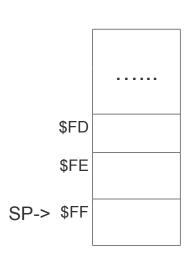

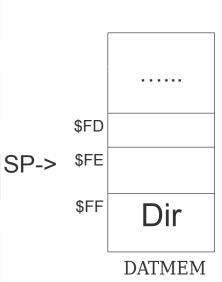

Antes de meter un nuevo dato, el SP contiene la dirección de la posición de la pila donde este se guardará.

Es como si se hiciera una pila de libros, el primero que quito es el último que he puesto. El primer dato se guarda en una posición determinada y el siguiente en la posición inmediatamente inferior. Nuestra pila crece hacia direcciones decrecientes de la memoria.

Supongamos SP=\$34

Representación abstracta de la zona de la memoria de datos y los valores del SP del CS2010

Proceso de guardar datos en la pila. Operación de PUSH

Proceso de guardar datos en la pila. Operación de PUSH

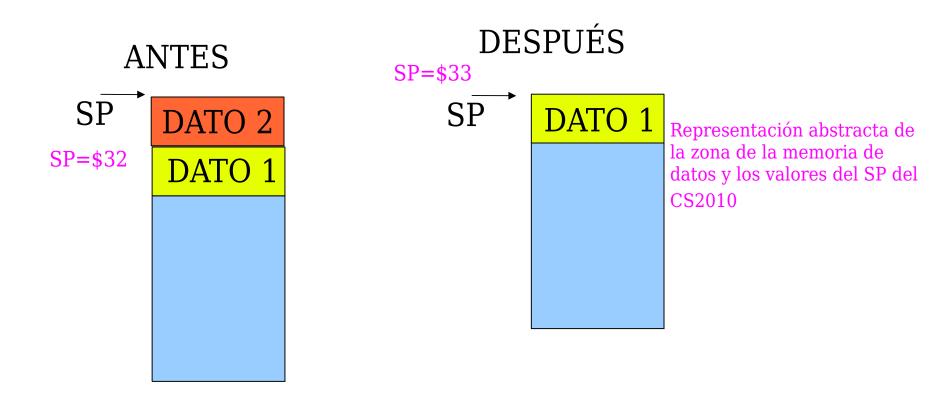

Proceso de extracción de datos de la pila. Operación de PULL. El primero que se lee es el último que se escribió.

Proceso de extracción de datos de la pila. Operación de PULL. El primero que se lee es el último que se escribió.

Decripción general:

Incrementar SP y guardarlo en MAR. Esto permite direccionar la posición que contiene la dirección de retorno.

Decripción general: Se accede a la pila y se recupera la dirección de retorno para volver a la instrucción siguiente a la de salto a subrutina.

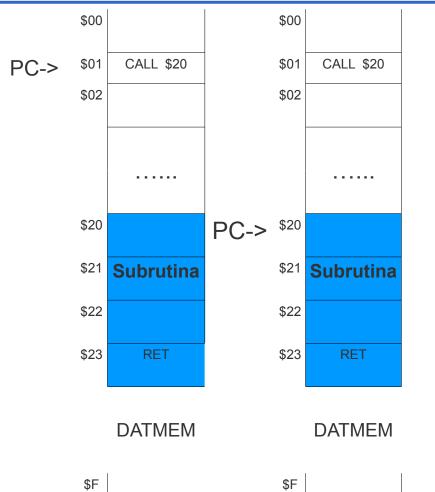

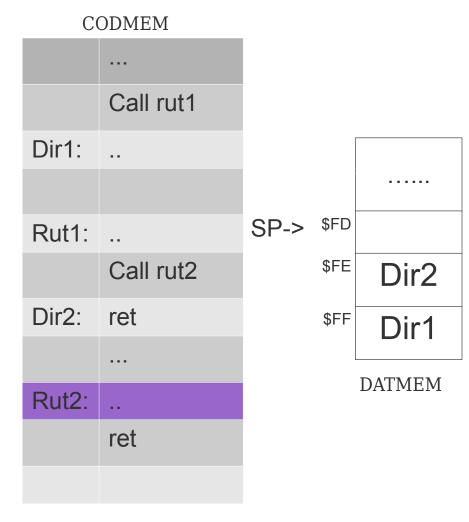

- Una subrutina es una secuencia de instrucciones que realizan una cierta tarea que es necesaria lleva a cabo en distintos puntos del programa.

- Cuando un programa necesita realizar la tarea, hace una llamada a la subrutina, ésta se ejecuta y cuando termina, el programa se reanuda por donde se había quedado (retorno de subrutina).

- Una subrutina se puede llamar todas las veces que el programa lo necesite

- Una subrutina puede llamar a su vez a otra subrutina: ejecución anidada de subrutinas

- Una subrutina puede llamarse a sí misma: subrutinas recursivas

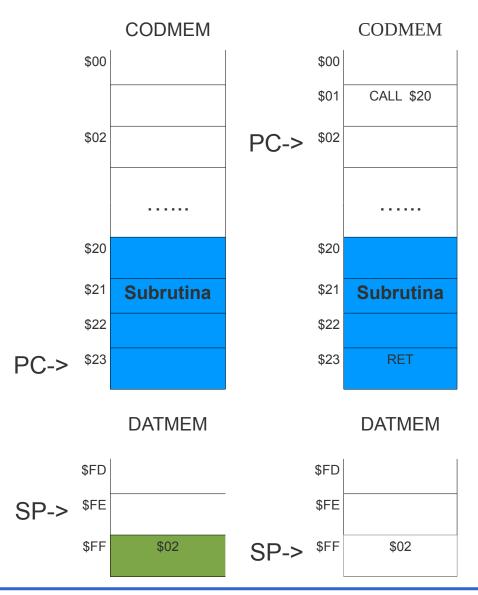

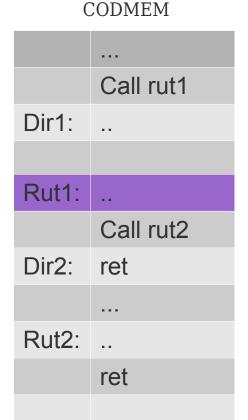

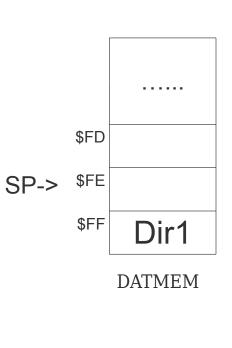

- Situación inicial (a). El computador ejecuta instrucciones y llega a CALL \$20.

- La ejecución de la instrucción CALL \$20 hace que:

- Se guarde en la pila el PC (que contiene \$02)

- Se "salte" a la dirección \$20

- Observe el comportamiento del puntero de pila o registro SP (b).

(b)

- Se ejecutan las instrucciones de la subrutina hasta que se procede a ejecutar la última instrucción o RET (c)

- La ejecución de RET hace que se saque el dato que está en la cima de la pila y que se guarde sobre el PC (d)

- A continuación se sigue ejecutando instrucciones. En este caso a partir de la dirección \$02.

- Observe que \$02 sigue en la PILA pero ya no es accesible y en la próxima operación de PUSH será sobreescrito.

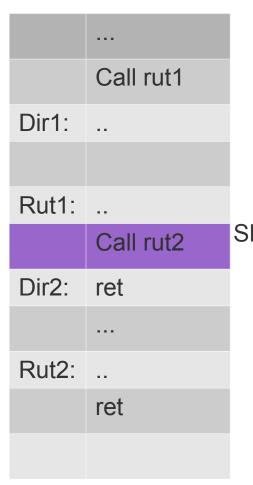

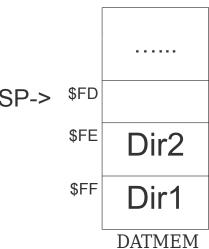

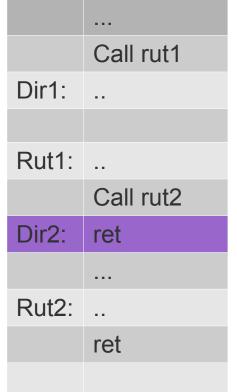

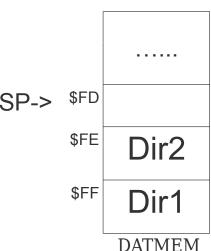

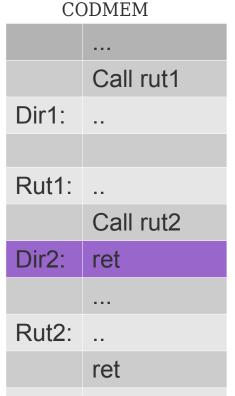

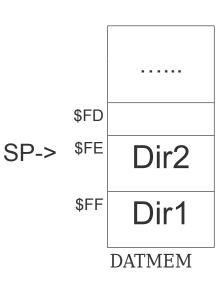

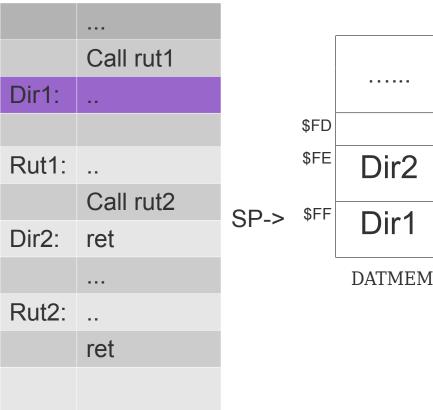

Anidamiento de subrutinas

|       | Call rut1 |

|-------|-----------|

| Dir1: |           |

|       |           |

| Rut1: |           |

|       | Call rut2 |

| Dir2: | ret       |

|       |           |

| Rut2: |           |

|       | ret       |

|       |           |

**DATMEM**

Anidamiento de subrutinas

#### Anidamiento de subrutinas

|       | Call rut1 |   |

|-------|-----------|---|

| Dir1: |           |   |

|       |           | ( |

| Rut1: | ••        |   |

|       | Call rut2 |   |

| Dir2: | ret       |   |

|       |           |   |

| Rut2: |           |   |

|       | ret       |   |

|       |           |   |

CODMEM

# Instrucciones de llamada y retorno de subrutinas

#### Anidamiento de subrutinas

|       | Call rut1 |   |

|-------|-----------|---|

| Dir1: |           |   |

|       |           | ( |

| Rut1: |           |   |

|       | Call rut2 |   |

| Dir2: | ret       |   |

|       |           |   |

| Rut2: |           |   |

|       | ret       |   |

|       |           |   |

# Instrucciones de llamada y retorno de subrutinas

#### Anidamiento de subrutinas

Observe que el orden en el que se deben extraer los contenidos del PC de la PILA debe ser en sentido inverso a como éstos se introdujeron en ella. (LIFO) CODMEM

# Modo inmediato

► El dato es parte del propio código de la instrucción y por tanto, tras finalizar el ciclo de búsqueda se encontrará en el registro IR.

# Códigos de condición de la instrucción de bifurcación condicional: BR\*\*

Los bits  $I_{10}I_{9}I_{8}$  codifican la condición de salto xx.

| I <sub>10</sub> | l <sub>9</sub> | <b>I</b> <sub>8</sub> | CONDICIÓN | nemónico(s)<br>de la condición | notas                                                                       |

|-----------------|----------------|-----------------------|-----------|--------------------------------|-----------------------------------------------------------------------------|

| 0               | 0              | 0                     | Z         | ZS, EQ                         | será cierta justo tras realizar la resta A-B si y solo si A=B               |

|                 |                |                       |           |                                | será cierta justo tras realizar la resta A-B si y solo si A <b< td=""></b<> |

| 0               | 0              | 1                     | С         | CS, LO                         | asumiendo notación base 2 sin signo                                         |

|                 |                |                       |           |                                | será cierta si y solo si el dato recién calculado no es                     |

| 0               | 1              | 0                     | V         | VS                             | representable en notación complemento a 2                                   |

|                 |                |                       |           |                                | será cierta justo tras realizar la resta A-B si y solo si A <b< td=""></b<> |

| 0               | 1              | 1                     | N xor V   | LT                             | asumiendo notación complemento a 2                                          |

| 1               | -              | -                     | ?         | -                              | estas condiciones no están definidas y no deben utilizarse                  |

BRZS, BREQ, BRCS, BRLO, BRVS, BRLT

| OP <sub>3</sub> | OP <sub>2</sub> | OP <sub>1</sub> | OP <sub>0</sub> | RESULT=                    | V <sub>out</sub> =                  | N <sub>out</sub> =  | Z <sub>out</sub> =             | C <sub>out</sub> = |

|-----------------|-----------------|-----------------|-----------------|----------------------------|-------------------------------------|---------------------|--------------------------------|--------------------|

| 0               | 0               | -               | 0               | -                          | V <sub>IN</sub>                     | N <sub>IN</sub>     | Z <sub>IN</sub>                | Θ                  |

| 0               | 0               | 0               | 1               | -                          | -                                   | -                   | -                              | -                  |

| 0               | 0               | 1               | 1               | -                          | V <sub>IN</sub>                     | N <sub>IN</sub>     | Z <sub>IN</sub>                | 1                  |

| 0               | 1               | 0               | 0               | SHR(A,C <sub>IN</sub> )    | C <sub>IN</sub> EXOR A <sub>0</sub> | RESULT <sub>7</sub> | NOT $OR_{i=0}^{7}(RESULT_{i})$ | A <sub>e</sub>     |

| 0               | 1               | 0               | 1               | SHL(A,C <sub>IN</sub> )    | $A_{7}$ EXOR $A_{6}$                | RESULT <sub>7</sub> | NOT $OR_{i=0}^{7}(RESULT_{i})$ | A <sub>7</sub>     |

| 0               | 1               | 1               | -               | Α                          |                                     | -                   | -                              | -                  |

| 1               | 0               | 0               | -               | (A + B) mod 2 <sup>8</sup> | overflow(A+B)                       | RESULT <sub>7</sub> | NOT $OR_{i=0}^{7}(RESULT_{i})$ | carry(A+B)         |

| 1               | 0               | 1               | -               | (A - B) mod 2 <sup>8</sup> | underflow(A-B)                      | RESULT,             | NOT $OR_{i=0}^{7}(RESULT_{i})$ | borrow(A-B)        |

| 1               | 1               | -               | -               | В                          | =                                   | -                   | -                              | -                  |

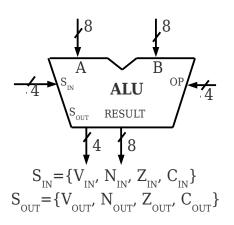

La ALU de este computador es mucho más compleja que la del CS2 debido a que ha sido la solución adoptada para poder realizar algunas de las nuevas instrucciones propuestas.

Esta solución de complicar la ALU no es la única opción.

A continuación justificaremos la complejidad de la ALU en base a las instrucciones añadidas.

| $S_{IN} = \{V_{IN},$     | , N <sub>IN</sub> , | Z <sub>IN</sub> , | $C_{IN}$        |

|--------------------------|---------------------|-------------------|-----------------|

| $S_{OUT} = \{V_{OUT'}\}$ | $N_{\text{OUT}}$    | $Z_{ou}$          | $_{T'} C_{OUT}$ |

| OP <sub>3</sub> | OP <sub>2</sub> | OP <sub>1</sub> | OP <sub>0</sub> | RESULT=                    | V <sub>out</sub> =                  | N <sub>out</sub> =   | Z <sub>out</sub> =             | C <sub>out</sub> =               |

|-----------------|-----------------|-----------------|-----------------|----------------------------|-------------------------------------|----------------------|--------------------------------|----------------------------------|

| 0               | 0               | -               | Θ               | -                          | V <sub>IN</sub>                     | $N_{_{\mathrm{IN}}}$ | Z <sub>IN</sub>                | 0                                |

| 0               | 0               | 0               | 1               | -                          | -                                   | -                    | -                              | -                                |

| 0               | 0               | 1               | 1               | =                          | V <sub>IN</sub>                     | N <sub>IN</sub>      | Z <sub>IN</sub>                | 1                                |

| 0               | 1               | Θ               | Θ               | SHR(A,C <sub>IN</sub> )    | C <sub>IN</sub> EXOR A <sub>0</sub> | RESULT,              | NOT $OR_{i=0}^{7}(RESULT_{i})$ | $A_{\scriptscriptstyle{\Theta}}$ |

| 0               | 1               | 0               | 1               | SHL(A,C <sub>IN</sub> )    | A <sub>7</sub> EXOR A <sub>6</sub>  | RESULT <sub>7</sub>  | NOT $OR_{i=0}^{7}(RESULT_{i})$ | A <sub>7</sub>                   |

| 0               | 1               | 1               | -               | A                          | -                                   | -                    | -                              | -                                |

| 1               | 0               | 0               | -               | $(A + B) \mod 2^8$         | overflow(A+B)                       | RESULT <sub>7</sub>  | NOT $OR_{i=0}^{7}(RESULT_{i})$ | carry(A+B)                       |

| 1               | 0               | 1               | -               | (A - B) mod 2 <sup>8</sup> | underflow(A-B)                      | RESULT <sub>7</sub>  | NOT $OR_{i=0}^{7}(RESULT_{i})$ | borrow(A-B)                      |

| 1               | 1               | -               | -               | В                          | -                                   | -                    | -                              | _                                |

¿Porqué necesitamos estas operaciones?

Instrucciones: *CLC* y *SEC*, ponen a 0 y 1 el flag de acarreo C La ALU no hace nada salvo cambiar este flag y dejar el resto inalterado. Vemos que en la ALU, además de entrar los 4 códigos de operación entran los 4 Flags.

| $S_{IN} = \{V_{IN},$         | N <sub>IN</sub> , | Z <sub>IN</sub> , | $C_{IN}$           |                 |

|------------------------------|-------------------|-------------------|--------------------|-----------------|

| $S_{_{OUT}} = \{V_{_{OUT'}}$ | $N_{\text{OUT}}$  | , Z <sub>ou</sub> | T, C <sub>OU</sub> | $_{\mathrm{T}}$ |

| OP <sub>3</sub> | OP <sub>2</sub> | OP <sub>1</sub> | OP <sub>0</sub> | RESULT=                    | V <sub>out</sub> =                  | N <sub>out</sub> =   | Z <sub>out</sub> =             | C <sub>out</sub> =               |

|-----------------|-----------------|-----------------|-----------------|----------------------------|-------------------------------------|----------------------|--------------------------------|----------------------------------|

| 0               | 0               | -               | 0               | -                          | V <sub>IN</sub>                     | $N_{_{\mathrm{IN}}}$ | Z <sub>IN</sub>                | 0                                |

| 0               | 0               | 0               | 1               | -                          | -                                   | -                    | -                              | -                                |

| 0               | 0               | 1               | 1               | -                          | V                                   | N <sub>IN</sub>      | Z <sub>IN</sub>                | 1                                |

| 0               | 1               | 0               | 0               | SHR(A,C <sub>IN</sub> )    | C <sub>IN</sub> EXOR A <sub>0</sub> | RESULT <sub>7</sub>  | NOT $OR_{i=0}^{7}(RESULT_{i})$ | $A_{\scriptscriptstyle{\Theta}}$ |

| 0               | 1               | 0               | 1               | SHL(A,C <sub>IN</sub> )    | A, EXOR A                           | RESULT,              | NOT OR, 7 (RESULT,)            | A <sub>7</sub>                   |

| 0               | 1               | 1               | -               | A                          | -                                   | -                    | -                              | -                                |

| 1               | 0               | 0               | -               | (A + B) mod 2 <sup>8</sup> | overflow(A+B)                       | RESULT <sub>7</sub>  | NOT $OR_{i=0}^{7}(RESULT_{i})$ | carry(A+B)                       |

| 1               | 0               | 1               | -               | (A - B) mod 2 <sup>8</sup> | underflow(A-B)                      | RESULT <sub>7</sub>  | NOT $OR_{i=0}^{7}(RESULT_{i})$ | borrow(A-B)                      |

| 1               | 1               | -               | -               | В                          | =                                   | =                    | =                              | -                                |

¿Porqué necesitamos estas operaciones? Instrucciones: ROR Rd y ROL Rd

Como vemos la ALU rota el dato que entra por su entrada A con la entrada de acarreo, ya que la tiene disponible como hemos dicho anteriormente. El dato rotado es lo que nos proporciona en RESULT.

¿Qué información nos proporcionan los flags?

**V:** La operación EXOR de  $C_{in}$  con  $A_0$  en el caso de desplazamiento a la dcha, y de  $A_7$  con  $A_6$  en el caso de desplazamiento a la izquierda. En este último se nos informa de un cambio de signo.

| $S_{IN} = \{V_{IN}, V_{IN}, V_$ | , N <sub>IN</sub> , | Z <sub>IN</sub> , | $C_{IN}$           |                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------------|--------------------|-----------------|

| $S_{OUT} = \{V_{OUT'}\}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $N_{OUT}$           | , Z <sub>ou</sub> | T, C <sub>OT</sub> | <sub>TT</sub> } |

| OP <sub>3</sub> | OP <sub>2</sub> | OP <sub>1</sub> | OP <sub>0</sub> | RESULT=                    | V <sub>out</sub> =                  | N <sub>out</sub> =   | Z <sub>out</sub> =             | C <sub>out</sub> = |

|-----------------|-----------------|-----------------|-----------------|----------------------------|-------------------------------------|----------------------|--------------------------------|--------------------|

| 0               | 0               | -               | 0               | -                          | V <sub>IN</sub>                     | $N_{_{\mathrm{IN}}}$ | Z <sub>IN</sub>                | 0                  |

| 0               | 0               | 0               | 1               | -                          | -                                   | -                    | -                              | -                  |

| 0               | 0               | 1               | 1               | -                          | V                                   | N                    | Ζ,,,                           | 1                  |

| 0               | 1               | 0               | 0               | SHR(A,C <sub>IN</sub> )    | C <sub>IN</sub> EXOR A <sub>0</sub> | RESULT <sub>7</sub>  | NOT $OR_{i=0}^{7}(RESULT_{i})$ | $A_{_{\Theta}}$    |

| 0               | 1               | 0               | 1               | SHL(A,C <sub>TN</sub> )    | A, EXOR A                           | RESULT,              | NOT OR, 7 (RESULT.)            | Α                  |

| 0               | 1               | 1               | -               | А                          | -                                   | -                    | -                              | -                  |

| 1               | 0               | 0               | -               | (A + B) mod 2 <sup>8</sup> | overflow(A+B)                       | RESULT <sub>7</sub>  | NOT $OR_{i=0}^{7}(RESULT_{i})$ | carry(A+B)         |

| 1               | 0               | 1               | -               | (A - B) mod 2 <sup>8</sup> | underflow(A-B)                      | RESULT <sub>7</sub>  | NOT $OR_{i=0}^{7}(RESULT_{i})$ | borrow(A-B)        |

| 1               | 1               | -               | -               | В                          | =                                   | =                    | -                              | -                  |

¿Porqué necesitamos estas operaciones? Instrucciones: ROR Rd y ROL Rd

¿Qué nos proporciona en los flags?

N: Bit más significativo de los números, nos informa del signo.

**Z:** Operación NOR de todos los bits del resultado. Vale 1 si el resultado es =0.

**C:** Bit que se desplaza.

| $S_{IN} = \{V_{IN}'$   | N <sub>IN</sub> , | Z <sub>IN</sub> , | $C_{IN}$                       |                 |

|------------------------|-------------------|-------------------|--------------------------------|-----------------|

| $S_{OUT} = \{V_{OUT'}$ | N <sub>out</sub>  | , Z <sub>ou</sub> | <sub>T</sub> , C <sub>OU</sub> | <sub>TT</sub> } |

| OP <sub>3</sub> | OP <sub>2</sub> | OP <sub>1</sub> | OP <sub>0</sub> | RESULT=                    | V <sub>out</sub> =                  | N <sub>out</sub> =  | Z <sub>out</sub> =             | C <sub>out</sub> = |

|-----------------|-----------------|-----------------|-----------------|----------------------------|-------------------------------------|---------------------|--------------------------------|--------------------|

| 0               | 0               | -               | 0               | -                          | V <sub>IN</sub>                     | N <sub>IN</sub>     | Z <sub>IN</sub>                | 0                  |

| Θ               | 0               | 0               | 1               | -                          | -                                   | -                   | -                              | -                  |

| 0               | 0               | 1               | 1               | -                          | V <sub>IN</sub>                     | N <sub>IN</sub>     | Z <sub>IN</sub>                | 1                  |

| 0               | 1               | 0               | 0               | SHR(A,C <sub>IN</sub> )    | C <sub>IN</sub> EXOR A <sub>0</sub> | RESULT,             | NOT $OR_{i=0}^{7}(RESULT_{i})$ | A <sub>e</sub>     |

| 0               | 1               | 0               | 1               | SHL(A,C <sub>IN</sub> )    | A, EXOR A                           | RESULT <sub>7</sub> | NOT OR 7 (RESULT,)             | A <sub>7</sub>     |

| 0               | 1               | 1               | -               | А                          | =                                   | =                   | =                              | -                  |

| 1               | Θ               | 0               | -               | (A + B) mod 2 <sup>8</sup> | overflow(A+B)                       | RESULT,             | NOT $OR_{i=0}^{7}(RESULT_{i})$ | carry(A+B)         |

| 1               | 0               | 1               | -               | (A - B) mod 2 <sup>8</sup> | underflow(A-B)                      | RESULT,             | NOT $OR_{i=0}^{7}(RESULT_{i})$ | borrow(A-B)        |

| 1               | 1               | -               | -               | В                          | -                                   | -                   | -                              | -                  |

Lo que entra por A lo direccionan los bits IR<sub>10-8</sub> fuente en ST (mirar arquitectura) ¿Porqué necesitamos esta operación? Instrucciones: ST (Rb), Rf; STS dirección, Rf; Los flags no importan. 10 formato registro fuente instrucción (registro con operando base en registro ST/LD) código de  $\mathbf{B}$ instrucción operación dato inmediato / dirección del con operando dato memoria o inmediato condición de dirección de salto instrucción salto de salto

|                                                          |                      |                   | 1                   |     |

|----------------------------------------------------------|----------------------|-------------------|---------------------|-----|

| C = UI                                                   | ът                   | 7                 |                     |     |

| $S_{IN} = \{V_{IN}\}$                                    | , IN <sub>IN</sub> , | L <sub>IN</sub> , | $C_{\rm IN}$        |     |

| $S_{OUT} = \{V_{OUT'}\}$                                 | N                    | . 7.              | . С                 | }   |

| $O_{\rm UIT}$ $ ($ $^{\prime}$ $O_{\rm UIT}$ $^{\prime}$ | OUT                  | , <b>–</b> oti    | <sub>гт</sub> , Оот | IΤJ |

| OP <sub>3</sub> | OP <sub>2</sub> | OP <sub>1</sub> | OP <sub>0</sub> | RESULT=                    | V <sub>out</sub> =                  | N <sub>out</sub> =  | Z <sub>out</sub> =             | C <sub>out</sub> = |

|-----------------|-----------------|-----------------|-----------------|----------------------------|-------------------------------------|---------------------|--------------------------------|--------------------|

| 0               | 0               | -               | 0               | -                          | V <sub>IN</sub>                     | N <sub>IN</sub>     | Z <sub>IN</sub>                | 0                  |

| 0               | 0               | 0               | 1               | -                          | -                                   | -                   | -                              | -                  |

| 0               | 0               | 1               | 1               | -                          | V <sub>IN</sub>                     | N <sub>IN</sub>     | Z <sub>IN</sub>                | 1                  |

| 0               | 1               | 0               | 0               | SHR(A,C <sub>IN</sub> )    | C <sub>IN</sub> EXOR A <sub>0</sub> | RESULT,             | NOT $OR_{i=0}^{7}(RESULT_{i})$ | A <sub>o</sub>     |

| 0               | 1               | 0               | 1               | SHL(A,C <sub>IN</sub> )    | A, EXOR A <sub>6</sub>              | RESULT <sub>7</sub> | NOT $OR_{i=0}^{7}(RESULT_{i})$ | A <sub>7</sub>     |

| 0               | 1               | 1               | -               | A                          |                                     | -                   | -                              | -                  |

| 1               | 0               | 0               | -               | (A + B) mod 2 <sup>8</sup> | overflow(A+B)                       | RESULT <sub>7</sub> | NOT $OR_{i=0}^{7}(RESULT_{i})$ | carry(A+B)         |

| 1               | 0               | 1               | _               | (A - B) mod 2 <sup>8</sup> | underflow(A-B)                      | RESULT <sub>7</sub> | NOT $OR_{1=0}^{7}(RESULT_{1})$ | borrow(A-B)        |

| 1               | 1               | _               | -               | В                          | -                                   | -                   | -                              | -                  |

Instrucciones que necesitan que un dato pase por la entrada B sin alterarse. El dato proviene de la pila de registros en el caso del registro base, lo direcciónan los bits IR<sub>2-0:</sub> o bien del registro IR si es una dirección o un dato inmediato (mirar arquitectura).

¿Porqué necesitamos esta operación? Instrucciones:**ST (Rb),Rf; STS dirección,Rf; LD Rd, (Rb); LDS Rd,dirección; CALL dirección, BRxx dirección; JMP dirección, LDI Rd,dato, MOV Rd,Rf** Los flags no se ven afectados.

| S.,,=          | ={V <sub>IN</sub> , | N.,, | Z,,, | C,,,} |   |

|----------------|---------------------|------|------|-------|---|

| $S_{OUT} = \{$ |                     |      |      |       | } |

| OP <sub>3</sub> | OP <sub>2</sub> | OP <sub>1</sub> | OP <sub>0</sub> | RESULT=                    | V <sub>out</sub> =                  | N <sub>out</sub> =   | Z <sub>out</sub> =             | C <sub>out</sub> = |

|-----------------|-----------------|-----------------|-----------------|----------------------------|-------------------------------------|----------------------|--------------------------------|--------------------|

| 0               | 0               | -               | 0               | -                          | V <sub>IN</sub>                     | $N_{_{\mathrm{IN}}}$ | Z <sub>IN</sub>                | Θ                  |

| Θ               | 0               | 0               | 1               | -                          | -                                   | -                    | -                              | -                  |

| 0               | 0               | 1               | 1               | -                          | V <sub>IN</sub>                     | $N_{_{\mathrm{IN}}}$ | Z <sub>IN</sub>                | 1                  |

| 0               | 1               | 0               | 0               | SHR(A,C <sub>IN</sub> )    | C <sub>IN</sub> EXOR A <sub>0</sub> | RESULT <sub>7</sub>  | NOT $OR_{i=0}^{7}(RESULT_{i})$ | Α <sub>Θ</sub>     |

| 0               | 1               | 0               | 1               | SHL(A,C <sub>IN</sub> )    | A <sub>7</sub> EXOR A <sub>6</sub>  | $RESULT_{_{7}}$      | NOT $OR_{i=0}^{7}(RESULT_{i})$ | A <sub>7</sub>     |

| 0               | 1               | 1               | -               | A                          | -                                   | -                    | _                              | -                  |

| 1               | 0               | 0               | -               | (A + B) mod 2 <sup>8</sup> | overflow(A+B)                       | RESULT <sub>7</sub>  | NOT $OR_{i=0}^{7}(RESULT_{i})$ | carry(A+B)         |

| 1               | 0               | 1               | -               | (A - B) mod 2 <sup>8</sup> | underflow(A-B)                      | RESULT <sub>7</sub>  | NOT $OR_{i=0}^{7}(RESULT_{i})$ | borrow(A-B)        |

| 1               | 1               | -               | -               | В                          | =                                   | =                    | -                              | -                  |

¿Porqué necesitamos esta operación? Instrucciones que necesitan suma.

Instrucciones: **ADD Rd,Rf; ADDI Rd,dato;**

V: desbordamiento en suma de números con signo.

N: MSB del resultado

**Z:** NOR del resultado indica si es cero

C: acarreo

| $S_{IN} = \{V_{IN},$                                                 | , N <sub>IN</sub> , | Z <sub>IN</sub> , | $C_{IN}$           |                |

|----------------------------------------------------------------------|---------------------|-------------------|--------------------|----------------|

| $\boldsymbol{S}_{\text{OUT}} \!\!=\! \{\boldsymbol{V}_{\text{OUT'}}$ | $N_{\text{OUT}}$    | $Z_{ou}$          | T' C <sub>OU</sub> | <sub>T</sub> } |

| OP <sub>3</sub> | OP <sub>2</sub> | OP <sub>1</sub> | OP <sub>0</sub> | RESULT=                    | V <sub>out</sub> =                  | N <sub>out</sub> =  | <b>Z</b> <sub>out</sub> =      | C <sub>out</sub> = |

|-----------------|-----------------|-----------------|-----------------|----------------------------|-------------------------------------|---------------------|--------------------------------|--------------------|

| 0               | 0               | -               | 0               | -                          | V <sub>IN</sub>                     | N <sub>IN</sub>     | Z <sub>IN</sub>                | Θ                  |

| 0               | 0               | 0               | 1               | -                          | -                                   | -                   | -                              | -                  |

| 0               | 0               | 1               | 1               | -                          | V <sub>IN</sub>                     | N <sub>IN</sub>     | Z <sub>IN</sub>                | 1                  |

| 0               | 1               | 0               | 0               | SHR(A,C <sub>IN</sub> )    | C <sub>IN</sub> EXOR A <sub>0</sub> | RESULT <sub>7</sub> | NOT $OR_{i=0}^{7}(RESULT_{i})$ | A <sub>o</sub>     |

| 0               | 1               | 0               | 1               | SHL(A,C <sub>IN</sub> )    | A <sub>7</sub> EXOR A <sub>6</sub>  | RESULT <sub>7</sub> | NOT $OR_{i=0}^{7}(RESULT_{i})$ | A <sub>7</sub>     |

| 0               | 1               | 1               | -               | A                          | -                                   | ı                   | -                              | -                  |

| 1               | Θ               | 0               | -               | $(A + B) \mod 2^8$         | overflow(A+B)                       | RESULT <sub>7</sub> | NOT $OR_{i=0}^{7}(RESULT_{i})$ | carry(A+B)         |

| 1               | 0               | 1               | -               | (A - B) mod 2 <sup>8</sup> | underflow(A-B)                      | RESULT <sub>7</sub> | NOT $OR_{i=0}^{7}(RESULT_{i})$ | borrow(A-B)        |

| 1               | 1               | -               | -               | В                          | _                                   | _                   | _                              | <u>-</u>           |

¿Porqué necesitamos esta operación? Instrucciones que necesitan resta.

Instrucciones: SUB Rd,Rf; SUBI Rd,Rf; CP Rd,Rf; CPI Rd,dato;

V: desbordamiento en suma de números con signo.

N: MSB del resultado

**Z:** NOR del resultado indica si es cero

**C:** borrow

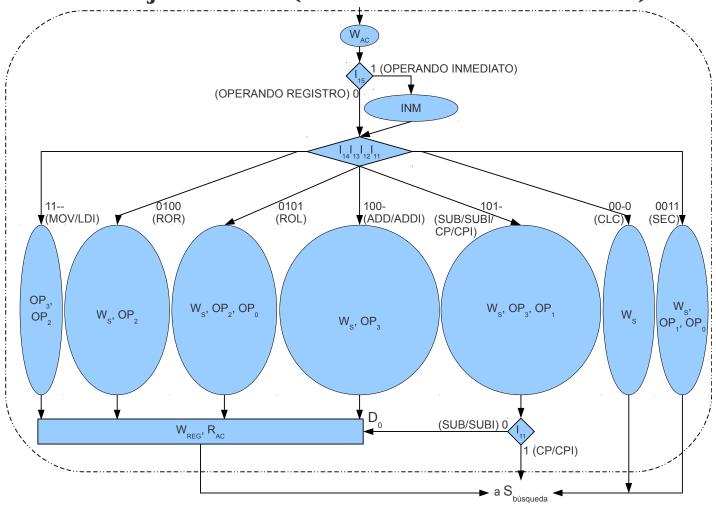

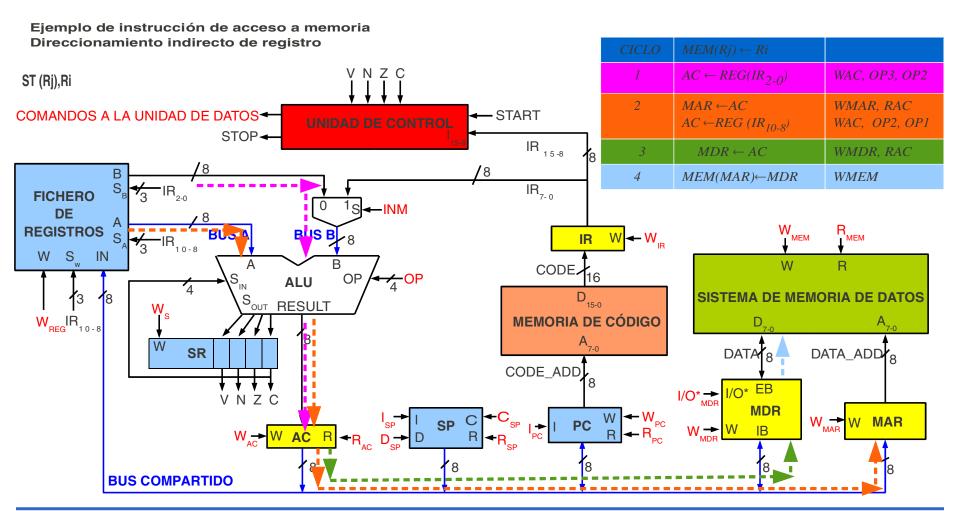

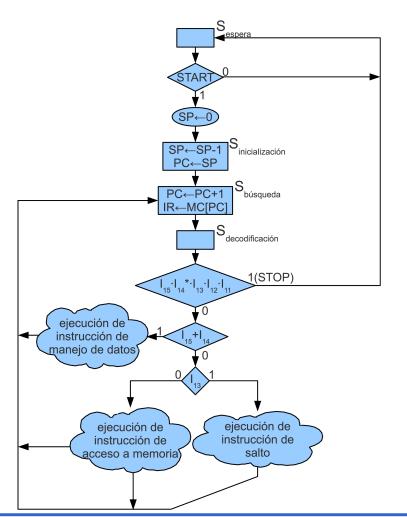

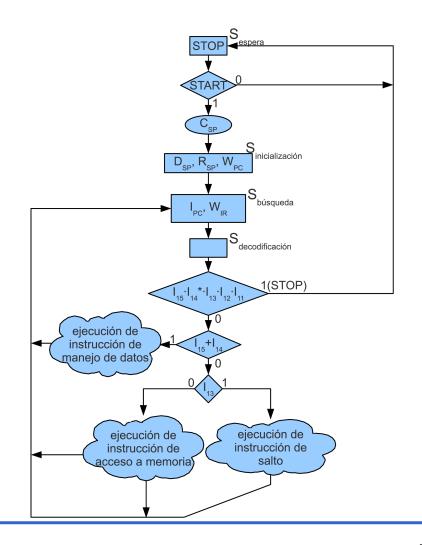

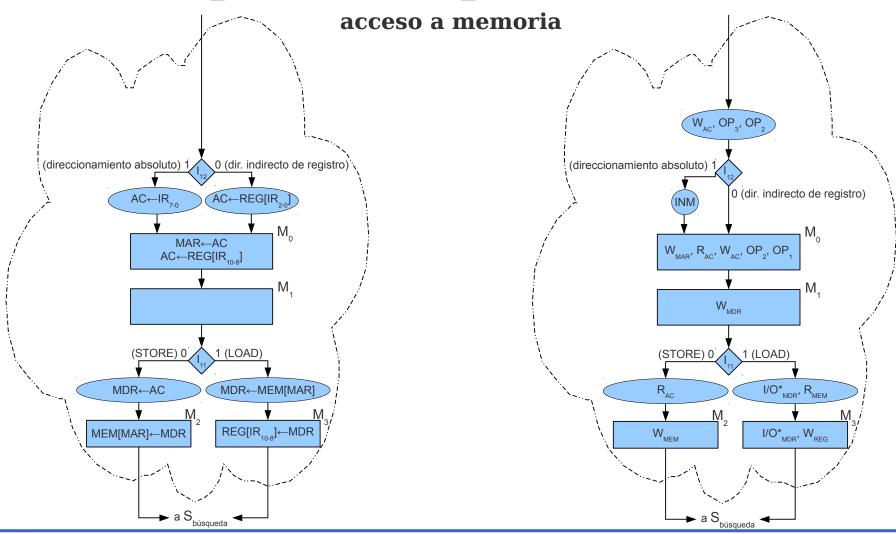

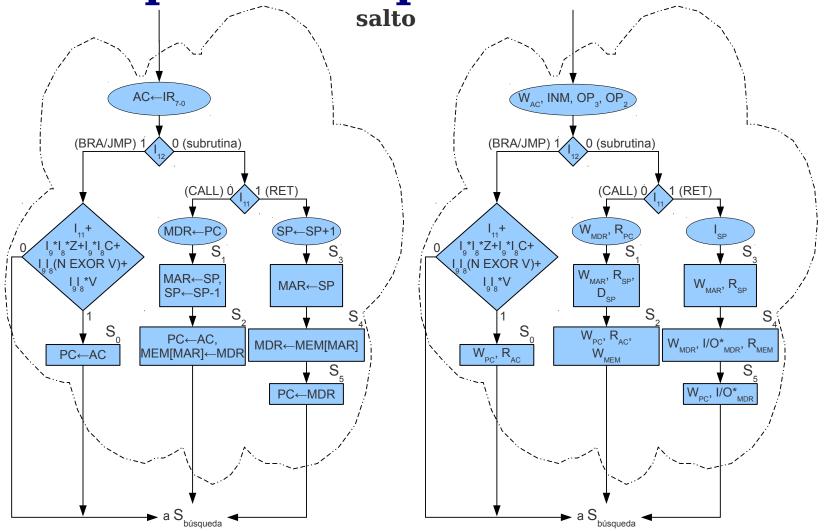

# Descomposición de las instrucciones en microoperaciones para algunos casos

# **Cartas ASM**

NOTA: La descripción RT del resto de las instrucciones se encuentra en un documento anexo a este. El alumno debe trabajar con ese documento.

Al final de este mismo documento se encuentran las cartas detalladas correspondientes a las descripciones RT de todas las instrucciones.

# Ejemplos de uso

Escriba una subrutina para el cálculo de la multiplicación mediante el algoritmo de sumas sucesivas.

MULT: LDI R0,0

CPI R2,0

BRZS RETORNA

BUCLE: ADD R0,R1

SUBI R2,1

BRZS RETORNA

JMP BUCLE

RETORNA: RET

# Ejemplos de uso

Escriba una subrutina que devuelva el mayor de dos números escritos en complemento a 2.

MAX: CP R1, R2

BRLT R1MENOR

MOV RO, R1

RET

R1MENOR: MOV R0, R2

RET

# Ejemplos de uso

Desarrolle una subrutina que escriba, de forma descendente, los números del 100 al 1 en una tabla situada a partir de la posición de memoria 123.

CUENTA: LDI R0,100

LDI R1,123

BUCLE: ST (R1), R0

ADDI R1,1 SUBI R0,1

BRZS RETORNA

JMP BUCLE

RETORNA: RET

- ► El CS 2010 no ha permitido solucionar unas de las deficiencias del CS2 planteadas al principio de este tema: la incapacidad de comunicación con el exterior.

- Dicho de otra forma: no posee capacidad de entrada salida (E/S).

- A continuación se expone un procedimiento que permitiría dotarlo de dicha capacidad.

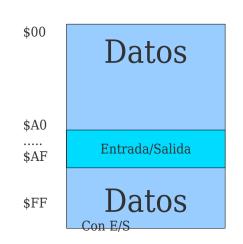

- Desde el punto de vista del programador la memoria es vista como una conjunto de posiciones de memoria; cada una de las cuales tiene asociada una dirección única.

- Parte del espacio de direccionamiento puede reservarse para que el procesador pueda acceder al exterior (entrada/salida mapeada en memoria).

- Reservaremos un subrango del espacio de direccionamiento (ej: \$A0-\$AF) para entrada/salida.

- Para ese subrango no se accede a la memoria de datos sino a los dispositivos de entrada/salida.

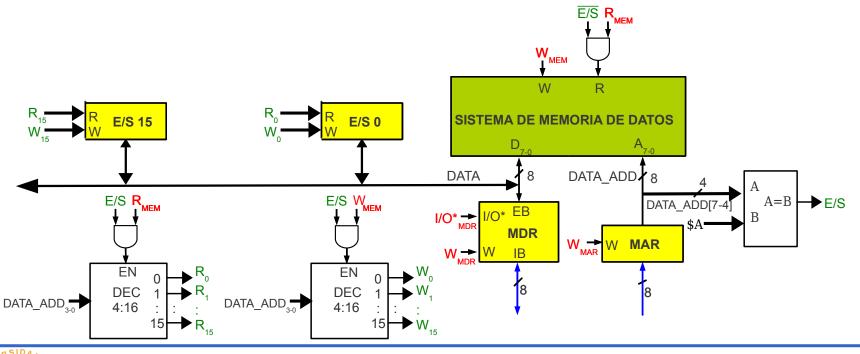

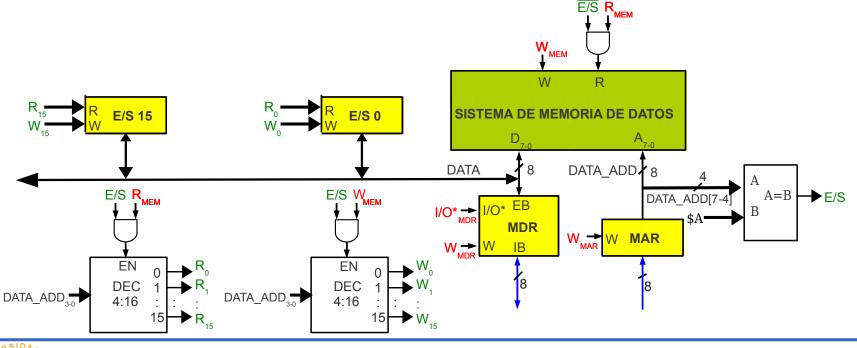

- Los cuatro bits más significativos de DATA\_ADD indican si la dirección pertenece al rango de entrada/salida .

- Para dicho rango, los bits restantes de DATA\_ADD se utilizarán para seleccionar la posición de E/S concreta.

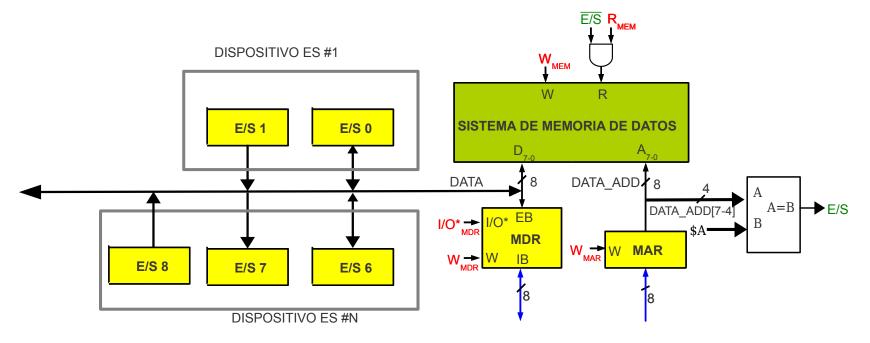

- Las posiciones de E/S puede ser de lectura/escritura, de sólo lectura o de solo escritura

- Un dispositivo de E/S puede agrupar varias posiciones de E/S.

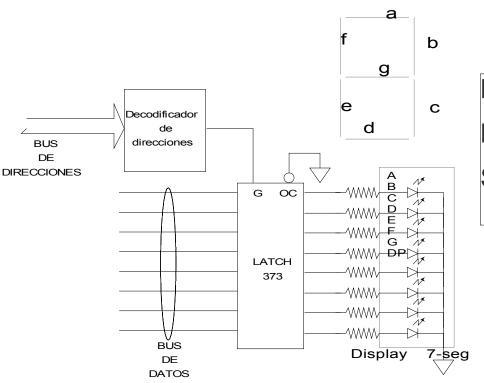

Dispositivo de salida (display de 7 segmentos)

LDI R0,\$A0 /\*Dirección del puerto de ES\*/

LDI R1,\$FF /\*Código 7seg del número 8\*/

ST (R0),R1 /\*Muestra el número 8\*/

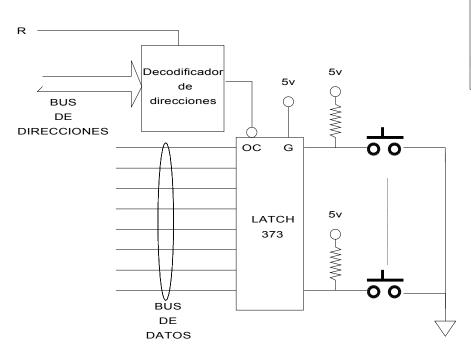

• Dispositivo de entrada (pulsadores)

LDI R0,\$A1 /\*Dirección del puerto de ES\*/

LD R1, (R0) /\*Almacena el estado de los pulsadores\*/

# **ANEXO: CARTAS ASM**

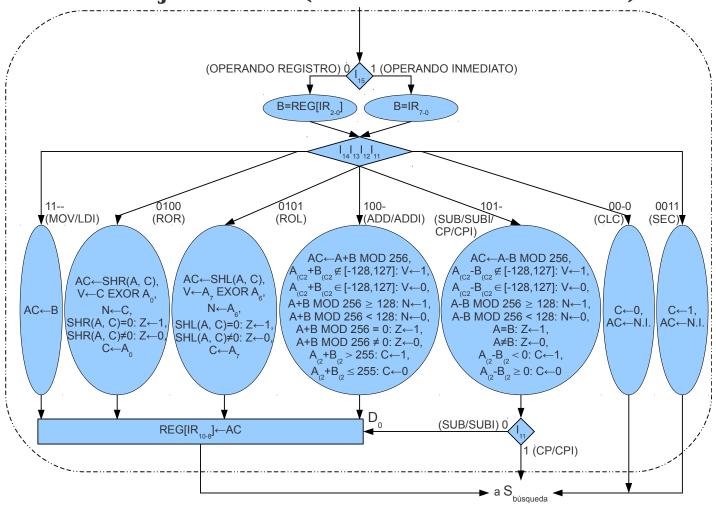

manejo de datos (trozo de la carta de datos)

manejo de datos (trozo de la carta de control)