The MTC is an initiative within the INVOMEC division

Industrialization &

Training in

Microelectronics

### Lab-exercise

## Lab 4:

# Implement and verify the complete system including a Uart

Cluster: Cluster2 Module: Module6b

Target group: Students

Version: 1.1 Date: 15/02/07

Author: Geert Vanwijnsberghe

Modified by:

This material was developed with support of the European Social Fund.

ESF: Prevent and combat unemployment by promoting employability, entrepreneurship, adaptability and equal opportunities between women and men, and by investment in people.

For Academic Use Only

©IMEC2005 www.mtc-online.be

#### The Microelectronics Training Center

#### Introduction

In this module, you implement your microprocessor on the XUP board and run the simple program developed in module 6a to reverse the characters in a string.

#### **Objectives**

After completing this module, you should be able to:

- Implement designs using ISE

- Configure FPGA devices

#### Knowledge background

· Basic knowledge of an FPGA design flow

#### Classification

- Level: 2

- Duration: 1 hour

#### Input

The solution of module6a and the system.ucf (inside the implementation folder) are actually used as input for this module.

#### The lab

- 1. Copy the complete input folder to <your\_module6b\_folder>.

- Start Xilinx ISE (Project navigator) by clicking on Xilinx ISE 8.2i → Project Navigator from the Start menu.

- 3. When another project is currently active, close it : File  $\rightarrow$  Close project

- 4. Create a new project: File → New Project...

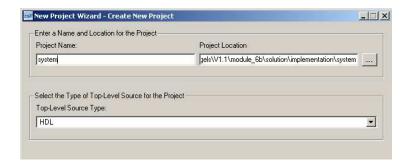

- In the New Project window, enter a Project Name "system" and choose the <your\_module6b\_folder>/implementation as the Project Location.

For Academic Use Only

Lab4Mod6bV1.1\_E.doc <u>www.mtc-online.be</u> 2/21

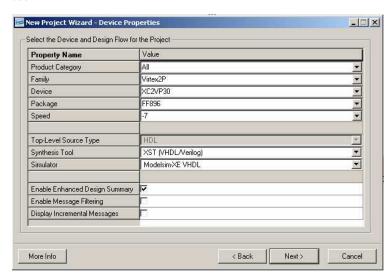

Click Next. In the next window, select the Family, Device etc...for the Project as shown below.

- Click Next. You don't need to create any new sources, so skip this window by clicking Next again.

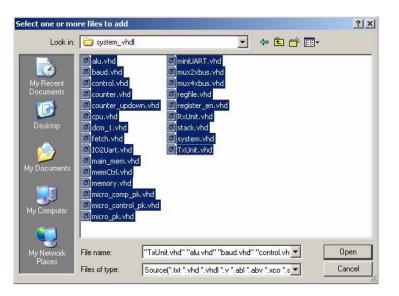

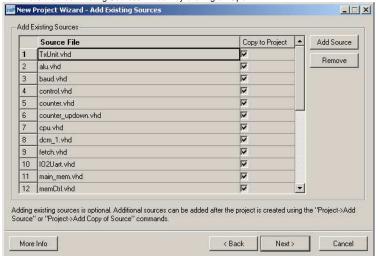

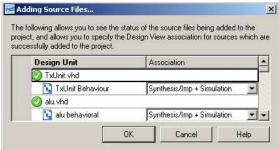

- In the current window, you Add Existing Sources. Press the Add Source button. Browse

to the directory where the design files are stored (system\_hdl) and select all .vhd files.

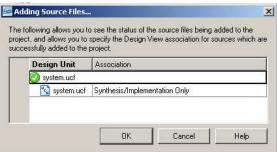

9. Terminate the Add Existing Sources window by clicking on Open.

Click next

10. Now you get a summary of all the files that are copied to your project. Click **Finish**.

| For Academic Use Only |                   |      |  |  |

|-----------------------|-------------------|------|--|--|

| Lab4Mod6bV1.1_E.doc   | www.mtc-online.be | 4/21 |  |  |

#### Click OK.

Lab4Mod6bV1.1 E.doc

For Academic Use Only

For Academic Use Only

www.mtc-online.be

5/21

Lab4Mod6bV1.1\_E.doc

www.mtc-online.be

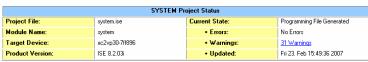

You are now back at the design summary. Xilinx - ISE - D:\Lab4\_microprocessor\Engels\V1.1\module\_6b\solution\im =IDX \_ | 8 | × OCKERE DE FPGA Design Summary \_\_\_\_\_\_ SYSTEM Project Status **Current State** Module Name - IOB Properties

- Timing Constraints

- Pinout Report

- Clock Report - € xc2vp30-7ff896 Target Device: кс2ур30-7ff896 ii- Q : system - struct (system vhd) Fri 23, Feb 13,49,43 2007 Product Version ISE 8 2 03 Updated: Errors and Warnings - Synthesis Messages

- Translation Messages

- Map Messages

- Place and Route Mes No partition information was found Report Name Generated Timing Messages

Bitgen Messages Translation Report All Current Mess

Detailed Reports - Synthesis Report

- Translation Report

- Map Report Place and Route Repo Static Timing Report Bitgen Report - Map Report

- Place and Route Rep

- Static Timing Report

- Bitgen Report Report Name Sources Snapshots Libraries Xplorer Report - DE Enable Enhanced Design Enable Enhanced Design

Enable Message Filtering

Display Incremental Messar

nhanced Design Summary Conte Add Existing Source

Create New Source

View Design Summary Design Utilities

User Constraints

Synthesize - XST

Implement Design - Show Warnings

- Show Failing Constraints

- Show Clock Report Implement Generate Programming Update Bitstream with Generate Programming File Processes Started : "Launching Design Summary". Console Errors Warnings Tcl Console M Find in Files

12. In the sources window you can expand system (hit the + sign before system-struct). If you also expand mem1 you will see that there is still a ? before the internal blockRAM.

6/21

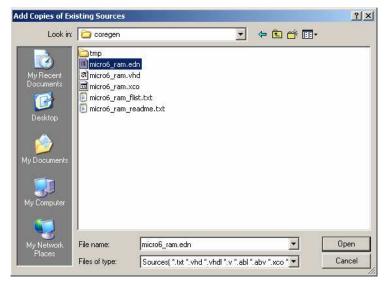

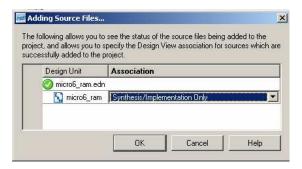

13. Add the edif description of the blockRAM that was created in the previous module 6a as shown in the next figures. At the end you will see that the question mark before the blockRAM has been replaced by an edif icon.

For Academic Use Only

7/21

8/21

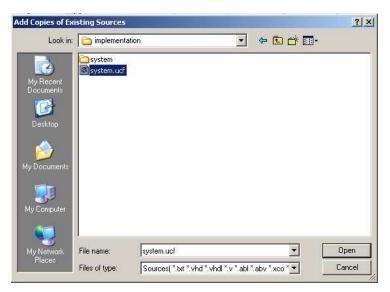

14. Before we can start the synthesis and implementation of the design into the FPGA we still have to specify the constraints. In this design the only constraints that we will apply are: mapping of the IO pins of system to the IO pads of the FPGA and the frequency of the clock. These constraints were written in system.ucf. Add this constraints file to system as follows:

15. Browse to the implementation folder and choose system.ucf and click Open.

For Academic Use Only

Hit **OK** and system.ucf will be added in the Sources window.

Lab4Mod6bV1.1 E.doc

16. Now you are ready to implement your design. Choose the top level of your design in the **Sources** pane. In this case, it is system-struct (system.vhd). Double-click

Xilinx ISE synthesizes the design and performs placement and routing and then generates the programming file. This procedure takes 3 to 5 minutes.

For Academic Use Only

www.mtc-online.be 11/21

For Academic Use Only

Lab4Mod6bV1.1\_E.doc

www.mtc-online.be

12/21

| SYSTEM Partition Summary            |

|-------------------------------------|

| No partition information was found. |

| Device Utilization Summary                     |         |           |             |         |  |

|------------------------------------------------|---------|-----------|-------------|---------|--|

| Logic Utilization                              | Used    | Available | Utilization | Note(s) |  |

| Number of Slice Flip Flops                     | 1,514   | 27,392    | 5%          |         |  |

| Number of 4 input LUTs                         | 2,922   | 27,392    | 10%         |         |  |

| Logic Distribution                             |         |           |             |         |  |

| Number of occupied Slices                      | 2,233   | 13,696    | 16%         |         |  |

| Number of Slices containing only related logic | 2,233   | 2,233     | 100%        |         |  |

| Number of Slices containing unrelated logic    | 0       | 2,233     | 0%          |         |  |

| Total Number 4 input LUTs                      | 2,935   | 27,392    | 10%         |         |  |

| Number used as logic                           | 2,922   |           |             |         |  |

| Number used as a route-thru                    | 1       |           |             |         |  |

| Number used as 16x1 RAMs                       | 12      |           |             |         |  |

| Number of bonded IOBs                          | 4       | 556       | 1%          |         |  |

| IOB Flip Flops                                 | 1       |           |             |         |  |

| Number of PPC405s                              | 0       | 2         | 0%          |         |  |

| Number of Block RAMs                           | 8       | 136       | 5%          |         |  |

| Number of MULT18X18s                           | 1       | 136       | 1%          |         |  |

| Number of GCLKs                                | 2       | 16        | 12%         |         |  |

| Number of DCMs                                 | 1       | 8         | 12%         |         |  |

| Number of GTs                                  | 0       | 8         | 0%          |         |  |

| Number of GT10s                                | 0       | 0         | 0%          |         |  |

| Total equivalent gate count for design         | 570,268 |           |             |         |  |

| Additional JTAG gate count for IOBs            | 192     |           |             |         |  |

| Performance Summary |                               |              |               |  |  |

|---------------------|-------------------------------|--------------|---------------|--|--|

| Final Timing Score: | 0                             | Pinout Data: | Pinout Report |  |  |

| Routing Results:    | All Signals Completely Routed | Clock Data:  | Clock Report  |  |  |

| Timing Constraints: | All Constraints Met           |              |               |  |  |

Have a look at the design summary. There should be no errors, the 4 IOs have to be bonded, all the signals have to be routed and all constraints should be met.

When ready, connect the USB cable and the serial cable of the XUP board with your PC. Now switch on the power of the board. You should get a message that an USB device has been detected.

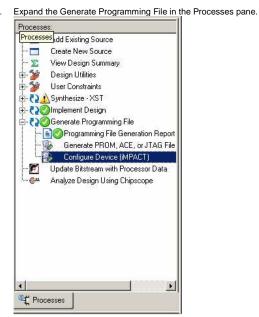

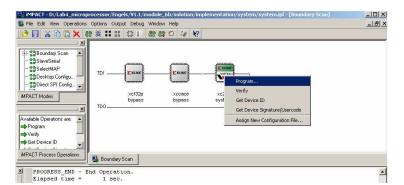

- 20. Double-click the **Configure Device (IMPACT)** process in the Processes pane.

- IMPACT starts and the Configure Devices window is displayed. Click Next without changing the default settings.

For Academic Use Only

Lab4Mod6bV1.1\_E.doc <u>www.mtc-online.be</u> 14/21

Click Finish.

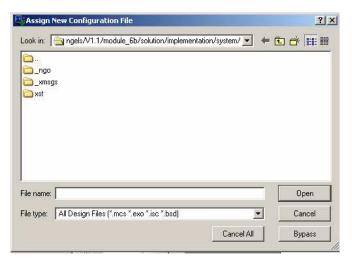

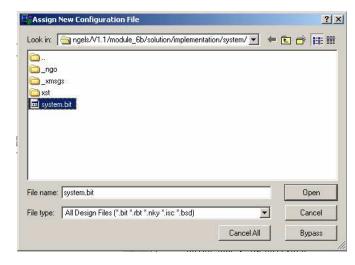

For the first 2 devices, click Bypass when the Assign New Configuration File window is displayed.

23. The third device is the target FPGA. Choose the file system.bit and click Open.

24. Add Virtex-II Pro/Virtex 4 Object Files window is displayed. Click OK.

For Academic Use Only

Lab4Mod6bV1.1\_E.doc

www.mtc-online.be

15/21

For Academic Use Only

Lab4Mod6bV1.1\_E.doc

www.mtc-online.be

16/21

25. Accept the following Warning message.

Lab4Mod6bV1.1 E.doc

26. Right-click the FPGA device and select **Program** to start the configuration.

For Academic Use Only

www.mtc-online.be

17/21

- Accept the default settings in the Program Options window.

Now you get a programmed successfully message.

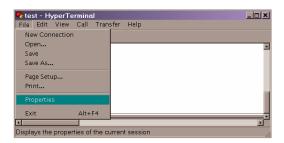

- 28. Start **HyperTerminal** from the Start Menu by choosing **Programs** → **Accessories** → **Communications** → **HyperTerminal**.

- In the Connection Description window, enter test as the Name of the connection and click OK.

30. Click **OK** to accept the default setting in the **Connect To** window.

For Academic Use Only

Lab4Mod6bV1.1\_E.doc <u>www.mtc-online.be</u> 18/21

31. In the **COM1 Properties** window do the following changes: Bits per second: 115200

Flow Control: None

Lab4Mod6bV1.1 E.doc

Leave the remaining settings unchanged and click **OK**.

32. Click on File → Properties in the main window of HyperTerminal.

For Academic Use Only

www.mtc-online.be

19/21

Choose the Settings tab in the test Properties window. Press ASCII Setup button and check Echo typed characters locally. Click OK. Dismiss the Properties window by clicking OK.

For Academic Use Only

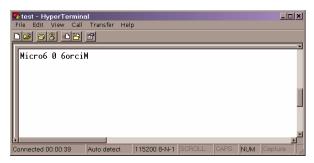

34. A connection with Micro6 is established. The program that Micro6 runs accepts a string of characters terminated by '0'. When '0' is received, Micro6 echoes the string you have entered after reversing the order of its characters.

# Congratulations!!!

35. You can restart the program by pressing the SW2 switch on the board.

|                     | For Academic Use Only |       |

|---------------------|-----------------------|-------|

| Lab4Mod6bV1.1_E.doc | www.mtc-online.be     | 21/21 |