The Microelectronics Training Center

# Introduction

# **Objectives**

After completing this module, you will be able to design elementary combinational circuits.

### Knowledge background

Basic VHDL knowledge

# Classification

- Level: 1

- Duration: 30 minutes

#### Input

- VHDL template of 2-input multiplexer (mux2bus.vhd).

- VHDL template of 4-inputer multiplexer (mux4bus.vhd).

# The lab

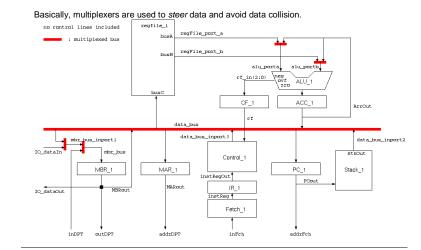

Multiplexers are combinational logic circuits. It is necessary to carefully cover all possible cases and include all relevant signals in the process sensitivity list (if you use a process). Deviation from these 2 rules may result in latches being generated and undesirable or unpredictable behavior

| 2014101             | For Academic Use Only |     |  |  |

|---------------------|-----------------------|-----|--|--|

| Lab4Mod1dV1.1_E.doc | www.mtc-online.be     | 2/4 |  |  |

Training Center The MTC is an initiative within the INVOMEC division

Microelectronics

The

Industrialization & Training in Microelectronics

# Lab-exercise

# *Lab 4: VHDL basics: multiplexers*

Cluster: Cluster1 Module: Module1d

Target group: Students

Version: 1.0 Date: 21/03/06 Author: Osman Allam Modified by: Geert Vanwijnsberghe History : 4/12/06 : testbench added

This material was developed with support of the European Social Fund. ESF: Prevent and combat unemployment by promoting employability, entrepreneurship, adaptability and equal opportunities between women and men, and by investment in people. http://www.esf-agentschap.be

MTC

For Academic Use Only

www.mtc-online.be

©IMEC2005

Multiplexers can be modelled VHDL in one of the following two ways: **1. Concurrent statements:** A multiplexer can be a signal concurrent conditional signal assignment statement.

Example: 2-input multiplexer

-- ports

```

A, B : in bit_vector (7 downto 0);

Outp : out bit_vector (7 downto 0);

Sel : in bit;

...

-- concurrent statement

outp <= A when sel = `0', B when sel = `1';</pre>

```

2. Sequential statements within a process:

A multiplexer can be a case statement or an if-statement inside a process. Example: 2-input multiplexer

Selecting bit type for the selection line (sel) is to demonstrate the concept simply. However, if you use std\_logic type (which should always be done), you have to take into account that a std\_logic signal may take any of 9 possible values. Thus the first example has to be re-writen to cover all possibilites as follows

-- ports

...

sel : in std\_logic;

...

-- concurrent statement

outp <= A when sel = `0', B when OTHERS = `1';</pre>

The second example doesn't have to be re-written (except changing the ports declaration) since "else" effectively covers all possibilities other than '0' in the if-condition. The same effect is

achieved by using 'OTHERS' in the concurrent assignment statement.

Exercise 1: 2-input multiplexer

Design a 2-input multiplexer. The inputs and output are unconstrained std\_logic\_vector. Use suitable width for the selection line(s). Implement your multiplexer as a case statement. Use the template provided in the file mux2bus.vhd.

| For Academic Use Only |                   | For Academic Use Only |                     |                   |     |

|-----------------------|-------------------|-----------------------|---------------------|-------------------|-----|

| Lab4Mod1dV1.1_E.doc   | www.mtc-online.be | 3/4                   | Lab4Mod1dV1.1_E.doc | www.mtc-online.be | 4/4 |

|                       |                   |                       |                     |                   |     |

#### Exercise 2: 4-input multiplexer

Design a 4-input multiplexer. The inputs and output are unconstrained std\_logic\_vector. Use a suitable width for the selection line(s). Implement your multiplexer as a case statement. Use the template provided in the file mux4bus.vhd.

Use the testbench tb\_mux to verify the multiplexers. This testbench does not contain automatic output comparison. This means that you have to verify the output manually.